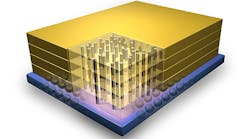

Three-dimensional integrated circuits (3D-ICs) help to increase power and performance, but not without the tradeoffs of increased complexity and associated challenges. A partnership between ANSYS and Fujitsu aims to limit those complications by leveraging the former’s power noise and reliability solutions to create 3D-ICs for high-performance central processing units (CPUs). Thanks to the full-chip capacity and fast turnaround time of ANSYS’ RedHawk and Sentinel platforms, Fujitsu can optimize IR drop, electromigration (EM), and thermal-reliability analysis of large processor designs.

Floorplanning for 3D-ICs requires the placement of through-silicon vias (TSVs) and a power/ground network. RedHawk allows for the exploration of various TSV placement options to meet the chips’ power noise and reliability requirements, which can be difficult to analyze and debug later in the design process. Specifically, RedHawk enables an IC-aware power noise analysis and sign-off package to ensure the tightest noise margin is met without wasted resources, as well as prevent failure risks.

Other key capabilities include SPICE-accurate transient simulation results at the SoC level using dynamic power models and simulation of 100 M+ instances with 2 B+ node designs that maintain flat sign-off accuracy. An out-of-box vectorless algorithm enables quick hotspot identification and high sign-off coverage, plus support for advanced device architectures such as sub-20-nm FinFETs.

The Sentinel platform, an I/O DDR power noise and timing analysis solution, helps minimize jitter and the impact of power/ground noise on DDR signal propagation. Design engineers can perform a time-domain solution of the entire DDR interface channel, including the bank of DDR buggers; on- and off-chip decoupling capacitors; and on-chip, package, and PCB interconnect parasitics. The software then predicts the impact of simultaneously switching noise on signal propagation and ensuing jitter.

Sentinel further creates I/O buffer models and on-die signal and power routing by using I/O layout information provided through RedHawk. The models capture the nonlinear, physical nature of the underlying circuits in a compact, SPICE-friendly format.