Cortus released the APS23 and APS25 32-bit processor IP cores, based on v2 of the company’s instruction set. The new instruction set aims to reduce the size of a system’s instruction memory, usually the largest single component in a system. The company says it is seeing an average of 16% improvement in code density over its v1 cores.

The Cortus v2 instruction set allows the seamless mixing of 16-, 24- and 32-bit instructions without mode switching. This instruction set is richer than the v1 instruction set, which employed a mix of 16- and 32-bit instructions. All C/C++ or assembler code developed for the v1 cores can be used unmodified on the v2 cores.

The APS23, which is the first product to use the v2 instruction set, is aimed at low-power, always-on/always-listening systems and those with less-demanding clock frequencies such as Bluetooth Smart. It features a Harvard architecture, sixteen 32-bit registers, a three-stage pipeline, and a sequential multiplier. It supports the AXI4-Lite bus as well as Cortus APS peripherals. The core delivers 2.83 DMIPS/MHz and 1.44 CoreMarks/MHz in computational performance. Dynamic power is 12 µW/MHz with a 90-nm process.

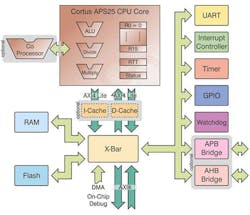

The APS25 core targets embedded systems demanding greater computational performance and system complexity. It supports co-processors or symmetric multiprocessing; up to eight co-processors can be added. The Cortus coprocessor interface allows licensees to add custom co-processors, for example, to accelerate computations in cryptography or signal processing, without knowing details of the core’s internals. Co-processor instructions inserted into C-code appear as function calls.

Incorporated into the APS25, which also features a Harvard architecture, are sixteen 32-bit registers, a five-stage pipeline, and a parallel multiplier. It supports the AXI4 bus as well as Cortus APS peripherals. APS25’s small size makes it particularly suitable for applications requiring two cores.