CTSD Precision ADCs (Part 3): Inherent Alias Rejection Made Possible (Download)

Part 1 of this series showcased a new class of easy-to-use, alias-free precision ADCs based on continuous-time sigma-delta (CTSD) architecture that offers simple, compact signal-chain solutions. Part 2 demystified the CTSD technology for signal-chain designers.

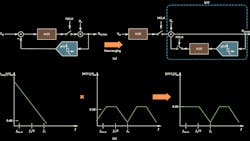

In Part 3, we compare the design complexity behind alias-rejection solutions for currently available precision ADC architectures. The article illustrates a theory to explain the inherent alias rejection of the CTSD ADC architecture. It also showcases how signal-chain design can be simplified and discusses the extended advantages of CTSD ADCs. Furthermore, it introduces new measurement and performance parameters to quantify alias rejection.