Pre-Silicon Power Verification for Power-Hungry Applications

This article is part of the TechXchange: Addressing Chip Verification Challenges

What you’ll learn:

- The drivers of innovation in power verification.

- The benefits of emulation to verify power.

- Key features to look for in an emulation solution.

5G. Hyperscale data centers. Mobile. Smart everything. These are just a few examples of today’s high-performance, power-hungry, or power-constrained applications. Missing your SoC power goals and power bugs on designs like these and others could pack a wallop on overall design success, your bottom line, and time to market. So, how do you optimize for peak and dynamic power and reduce leakage in this era? It’s time to shift left via fast power emulation technology and verify the power for designs pre-silicon.

Shifting the Focus in the Power-to-Performance Equation

Over the last 10 years, chip design has been about how fast chips could compute. Each gigahertz of speed represented billion-per-second core operations, a stand in for how fast the arithmetic logic units (ALUs) could process data. The higher the gigahertz, the better, which unfortunately also equates to more compute power consumption.

Historically, chip speed was measured by single- and double-digit percentage improvement rates. For instance, if a chip could run 10% or 20% faster than its predecessor or a competitor, that was considered pretty good.

Today, while clock speed isn’t increasing very much, next-generation chips can process many times more data than previous generations through massive parallelism, an entirely different scale of performance improvement. And, as the area of chips becomes smaller, the tradeoffs between compute performance and power are more substantive. That’s why in chip design, where achievements in performance are already vast, the conversation is shifting to include a bigger focus on power optimization.

Power-Hungry Designs Drive a New Frontier in Power Verification

Because today’s complex designs commonly have billions of gates, power management can be your Achilles heel. The bigger the design, the bigger the risk if you fall short in managing your power profile well. Some of the applications driving the conversation on power include self-driving cars, networking, mobile, virtual reality, and image recognition—anything that requires processing of massive amounts of data. Here are examples of why some key design categories are putting greater emphasis on power:

- GPUs: Running billions of clock cycles per second, power simulation that runs only at key points over time falls short.

- AI: Because artificial intelligence is so new, power profiling can be tricky, but it’s the holy grail for AI SoC designers to be able to tout both power efficiency and fast compute performance.

- 5G: Parallel processing at high frequencies—especially in radio-head semiconductors—makes power efficiency critical.

- Hyperscale data centers: Billions of gates and complexity in the software workload to boost data throughput to warp-speed levels, with energy efficiency, has put power management front and center.

- Mobile: Demand for battery-life longevity in a tiny form factor while performing complex, image-heavy tasks makes power efficiency critical in next-generation designs.

While it’s true that these applications have helped create the demand for the exponential leaps in processor speed and performance, they also demand innovation when it comes to power management.

In addition, the climate crisis is making the focus on power an existential one, bringing consumer and regulatory pressure to bear. All of this change requires a lens of precision on power verification—critical to optimizing your power budget and bringing power down.

Why Emulation is the Power Verification Answer for Next-Generation Designs

Designers typically have a phased approach to their work, including architectural exploration, register transfer level (RTL), physical design, and verification. Traditionally, power analysis with realistic software workloads could only be done post-silicon. The outcome of weeks of experimentation to approximate power consumption is heavily influenced by the experience of the engineer, as well as trial and error.

Looking for optimization opportunities in such a way is not only tedious and time-consuming, but accuracy in real-world scenarios is hit and miss. With large, dynamic applications, it’s impossible to simulate real-world workloads.

Let’s face it, it’s easier, quicker, and more budget-friendly to resolve your power issues earlier in the software development lifecycle. If you could detect the power-hungry activities and leakage, optimize dynamic power, and manage for peak power, it would help eliminate risk. Emulation pulls back verification to much earlier in the design process: pre-silicon.

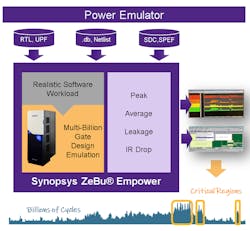

Emulation imitates the actual hardware behaviors and maps the design. It accurately shows the system activity flow so that designers can analyze and benchmark average power for an accurate power profile. Emulation speeds up verification by 1,000-fold over simulation, enabling an exhaustive number of test cycles—millions or even billions of cycles. The result is a much more accurate power profile, with diagnostics showing average power and the components where peaks are high.

Emulation that Can Verify Power in Hours, Pre-Silicon

Here are a few things to think about when choosing an emulation solution for power verification. A good emulation system should use real-life workloads pre-silicon and give you power verification within hours. Make sure the design size and emulation cycles can be parallelized, scaling design cycles and tying them to emulation cycles.

A software-driven, low-power emulation solution should reduce overall static and dynamic power consumption. And it will offer maximum compute performance in multiple iterations per day to deliver actionable results. You will be able to identify peak power and improve your design’s dynamic and leakage power profiles, easily and early.

Emulation solutions must use fast emulation hardware technologies for quick analysis. They should have adequate capacity and the ability to run in key modes for debugging and pass/fail accuracy (see figure).

What’s Next in the Power-Verification Game?

Gartner projects that new hyperscale data-center infrastructure spending will grow by 6% this year. Also this year, 5G infrastructure revenue will grow by 39%. The mobile-device install base will reach 6.2 billion devices, and with COVID normalizing a new world of remote everything as well as a hybrid work model, that growth can only continue. Finally, AI will generate $2.9 trillion in business value in 2021. Complex, high-performance, power-hungry applications are not only here to stay, but they’re also taking us to our future.

With big data only becoming bigger and fueling more applications, power is certainly the next big frontier in SoC designs. The good news is that more accurate, faster power analysis delivering actionable results sooner than ever before is available now. In the future, we can look forward to power analysis in multi-stages of design and development, including utilization of IP blocks with power-consumption models ready to go. With a focus on better methods for power management, the performance of power-hungry applications will only get better.

About the Author

Dr. Johannes Stahl

Senior Director, Product Marketing, Emulation, Synopsys

Dr. Johannes Stahl is a senior director of product marketing at Synopsys, where he is currently responsible for the Synopsys ZeBu® emulation and HAPS® prototyping business lines. Prior to Synopsys, he worked at CoWare and was responsible for virtual prototyping, processor design, signal processing, and ecosystem relationships. Prior to that, he led a design services team at Synopsys developing advanced wireless IP for the semiconductor industry. Johannes holds advanced degrees in electrical engineering from Aachen University, Germany.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: