Mentor debuts Tessent Connect and Tessent Safety at ITC

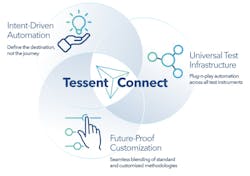

Mentor, a Siemens business, has introduced Tessent Connect, a design-for-test (DFT) automation methodology that delivers intent-driven hierarchical test implementation that helps IC design teams achieve manufacturing test quality goals faster and with fewer resources compared with traditional DFT methods. As part of the Tessent Connect rollout, Mentor also announced the Tessent Connect Quickstart program, offering detailed flow assessments from Mentor’s applications and consulting services engineers.

Mentor also introduced the Tessent Safety ecosystem, which leverages the comprehensive automotive IP portfolio of Arm as part of the company’s Functional Safety Partnership Program. As part of the Tessent Safety ecosystem, Mentor unveiled a new BIST solution delivering up to 10x faster in-system test than traditional offerings.

Tessent Connect

Today’s advanced IC designs can achieve very high defect coverage for manufacturing and in-system test by integrating dedicated on-chip infrastructure such as embedded compression, built-in self-test, and IEEE 1687Designed from the ground up to support hierarchical DFT, Mentor’s Tessent Connect automation approach helps eliminate these design inefficiencies. With Tessent Connect, IC designers interact with the Tessent software design tools using a higher level of abstraction, which describes the intended result rather than step-by-step instructions. The benefits of this abstraction-based approach include seamless collaboration across disparate DFT teams, plug-and-play reuse of IC components, significantly shorter turn-around times, and the automation of many time-consuming setup, connectivity, and pattern-generation tasks.

An early adopter of Tessent Connect is eSilicon, a provider of FinFET ASICs, market-specific IP platforms, and advanced 2.5D packaging solutions. Leveraging the advanced automation of Tessent Connect, eSilicon recently improved IC DFT implementation cost while enabling system-level DFT testing and debug capabilities for a highly sophisticated next-generation ASIC.

“eSilicon uses Tessent Connect to help us meet our aggressive production schedules and deliver industry-leading ICs like those based on eSilicon’s neuASIC 7-nm platform for machine learning,” said Joseph Reynick, director of DFT services at eSilicon. “As design complexity continues to grow, our system/OEM customers’ needs expand from just focusing on high-quality IC manufacturing test to also providing effective in-system test and functional debug capabilities. With today’s complex 2.5D/3D devices, we are not shipping in volume until our chips are fully operational in our customers’ systems, including DFT and IP test. It would be very difficult to meet these challenges without the Tessent DFT portfolio and the efficiencies gained from Tessent Connect automation.”

Part of the Tessent Connect rollout, Mentor’s new Tessent Connect Quickstart program offers expertise in delivering customized insights and services that help IC design teams fully optimize and automate their DFT processes when using Tessent Connect.

“Our customers are continuously looking to reduce their test implementation costs as their design sizes grow and quality requirements become more stringent,” said Brady Benware, vice president and general manager for the Tessent product family at Mentor, a Siemens business. “With Tessent Connect and the corresponding Quickstart program, our customers are empowered with an accelerated and automated path to DFT sign-off.”

For more information about Mentor’s Tessent product line, visit: https://www.mentor.com/products/silicon-yield/tessent/. In addition, attendees of the 2019 International Test Conference are invited to visit booth #401 for demonstrations of Tessent products and solutions.

Tessent Safety

The new Tessent software Safety ecosystem is a comprehensive portfolio of best-in-class automotive IC test solutions from Mentor with links to its industry-leading partners. The program helps IC design teams meet the increasingly stringent functional safety requirements of the global automotive industry. The Tessent Safety ecosystem provides a robust alternative to competing programs, which are based on closed, monolithic, single-source models. Mentor’s open ecosystem approach to IC test functional safety assurance allows chipmakers to combine Mentor’s IC test technologies with other best-in-class solutions, more complete, higher performing end-solutions.

Planned for rapid expansion via partnerships with Mentor’s roster of leading partners, the Tessent Safety ecosystem includes the following technologies:

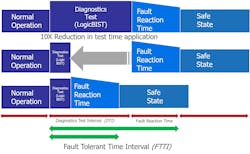

· Built-in self-test (BIST) technologies from Mentor, including the new Tessent LBIST with the Observation Scan Technology (LBIST-OST) solution designed to dramatically reduce run times for in-system monitoring of digital logic components in automotive ICs. Engineered to help customers meet stringent automotive functional safety requirements, the new Tessent LBIST-OST solution delivers up to a 10x reduction of in-system test time compared to traditional logic BIST technologies.

· The Tessent™ MemoryBIST, which features a comprehensive automation flow that provides design rule checking, test planning, integration, and verification at either the RTL or gate level. Because Tessent MemoryBIST features a hierarchical architecture, BIST and self-repair capabilities can be added to individual cores as well as at the top level.

· The Tessent MissionMode product, which provides a combination of automation and on-chip IP for enabling semiconductor chips throughout an automotive electronics system to be tested and diagnosed at any point during a vehicle’s functional operation.

· The Tessent DefectSim transistor-level defect simulator for analog, mixed-signal (AMS) and non-scan digital circuits. Suitable for both high-volume and high-reliability ICs, Tessent DefectSim measures defect coverage and tolerance.

· Mentor’s participation in the Arm Functional Safety Partnership Program (AFSPP). The Mentor Tessent Safety ecosystem leverages Arm Safety Ready IP functionalities like the Cortex-R52 processor, which combines real-time execution with the highest level of integrated functional safety capabilities of any Arm processor, as well as advanced hypervisor technology to simplify software integration, and robust separation functionality to protect safety-critical code.

· Mentor’s automotive-grade automatic test pattern generation (ATPG) technology, which detects defects at the transistor and interconnect levels often missed by traditional test patterns and fault models.

· Close links to Mentor’s Austemper SafetyScope and KaleidoScope products, which add state-of-the-art safety analysis, auto-correction and fault simulation technology to address random hardware faults. Austemper technology analyzes a designer’s RTL for faults and vulnerabilities and is capable of smart fault injection to help safety mechanisms react in a planned manner for covered faults. Through parallelized and distributed operation methods, proprietary acceleration algorithms are used to achieve speed-ups of many orders of magnitude over standard gate-level fault injection techniques.

Among the early adopters of key technologies in Mentor’s Tessent Safety ecosystem is Renesas, which evaluated Mentor’s new Tessent LBIST-OST solution in designing one of its newest automotive processors.

“Leveraging the Observation Scan technology featured in the new Tessent LBIST-OST solution, we were able to reduce the test time for in-system Logic BIST by 5x, thereby enabling a much faster coverage ramp up,” said Hideyuki Okabe, director, Digital Design Technology Department, Shared R&D EDA Division, IoT and Infrastructure Business Unit at Renesas Electronics Corporation. “This enabled us to reduce our Fault Tolerant Time Interval (FTTI) when using Logic BIST as a safety mechanism and improve the safety response when detecting new defects in our automotive products. We hope to continue to adopt this technology going forward for our automotive products."

The Mentor Tessent products in the Tessent Safety ecosystem are part of the Mentor Safe program, which is one of the industry’s broadest and most comprehensive ISO 26262 qualification programs. For more information about the Mentor Safe program, visit: https://www.mentor.com/mentor-automotive/functional-safety.

See Evaluation Engineering's January issue for more on Tessent Connect and Tessent Safety.

About the Author

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: