IAR Systems is known for its IAR Embedded Workbench along with a host of security and embedded development tools like the Visual State state-machine model development toolkit. The company complements these with evaluation kits that highlight the hardware and its software.

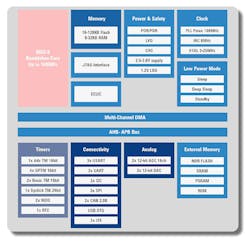

The focus of this article is the IAR RISC-V GD32V evaluation board built around the GigaDevice Semiconductor GD32VF103 microcontroller (Fig. 1). This micro has up to 128 kB of on-chip flash memory compared to the SiFive HiFive RISC-V chip I previously reviewed, which used an off-chip SPI flash chip for application code.

The GD32VF103 is based on the Bumblebee core. This is the same core used by Andes Technology’s AndeStar V5 chip. The Bumblebee core supports the RV32IMAC instruction set. This means that it’s a 32-bit integer core (RV32I) with multiply/divide (M), atomic instructions (A), and compressed instruction (C) support. The system employs a two-stage variable-length pipeline architecture.

The platform’s register file includes 32 registers; the 32-bit instructions are the norm with 16-bit compressed instructions, too. It’s very similar to other popular 32-bit microcontroller architectures. The compressed 16-bit instructions can result in a 25% to 30% reduction in code size.

The 32-bit chip runs at 108 MHz and has the usual complement of micro peripherals. This includes multiple timers, UARTs, SPI, I2C, I2S and an external memory controller. Dual CAN 2.0B controllers and a USB 2.0 OTG controller are incorporated. There’s a mix of RISC-V 16- and 24-bit timers as well, plus GigaDevice adds a 64-bit real-time timer. Analog peripherals include a 1-Msample/s ADC; dual 12-bit, 16-channel ADCs; and dual 12-bit DACs. Versions are available with up to 80 GPIOs.

The system needs a power supply from 2.6 to 3.6 V dc and has 5-V-tolerant I/O pins. It features multiple low power modes and a standby current requirement of 6.3 µA. Package options include QFN36, LQFP48, LQFP64, and LQFP100. Among the available development tools are Nuclei Studio, IoT Studio, and SEGGER Embedded Studio in addition to the IAR Embedded Workbench. It’s compatible with a variety of operating systems, such as μC/OS II, FreeRTOS, RT-Thread, TencentOS-tiny, and LiteOS.

Getting Started

The biggest kicker is that the IAR Embedded Workbench comes with a 30-day license. That’s usually enough time to determine if the software platform is what you need, assuming you can dedicate enough time to your evaluation. I have three days left on my license to wrap up this article, which is cutting it a bit tight. There’s an IAR plug-in for the open source Eclipse IDE, but it requires Workbench to be installed. At this point, the RISC-V support was not in the list of installations, so I couldn’t investigate the level of support.

On the plus side, getting the system up and running takes just a couple hours. The software installation on Windows is trivial as expected. The board comes with IAR’s I-Jet Lite (Fig. 2), which provides a JTAG interface to the board.

The eval board has a host of interfaces including undedicated LEDs and switches. It provides a 3D accelerometer, a potentiometer connected to an ADC, a light sensor, temperature and humidity sensors, an on-board microphone, and an iPhone-compatible earbug jack. This is an SPI flash memory as well for off-chip data storage. There’s a USB connection for a serial port. The I-Jet Lite also uses a USB connection.

In addition, you can solder headers to through-holes that will provide an Arduino-compatible interface. I haven’t tried doing this yet.

The software installation includes a host of sample C applications that exercise the various peripherals. Three jumpers need to be adjusted for different LED and peripheral combinations. The comments in the code outline the proper settings.

Running through the code examples takes an afternoon. The template project is the best starting point for building up new applications. There’s also an EMBC CoreMark application if you’re into performance numbers. It kicks out a result around 360, which is on par with an Arm Cortex-M3, depending on whose Arm-based chip you’re looking at.

Building Better Code

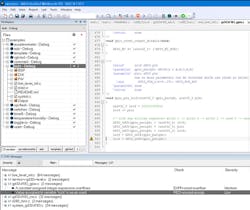

The IAR Embedded Workbench comes with IAR’s C/C++ compiler. It maintains support for more than the typical open-source C/C++ compiler, such as MISRA C and IAR’s C-STAT static-analysis tool (Fig. 3). C-STAT adds MISRA C++ support. It also maps checks to Common Weakness Enumeration (CWE) issues.

If you want to write better C code, then including MISRA C is a good idea. The Workbench provides fine grain control of the rules that are enabled. It defaults to the required set, but you can add or remove them at will.

I did try out MISRA C and C-STAT on the sample applications. It’s obvious this wasn’t done by IAR, as each project kicks out hundreds of notifications. This is typical—the majority of C/C++ programmers don’t follow these rules, but most tend to be trivial details. For example, disabling a few of the rules like 2.2, 5.1, and 16.5 significantly reduces the number of notifications.

The use of single-line comments is where rule 2.2 comes in; limiting the number of characters in a symbol to 51 is rule 5.1. The use of f() versus f(void) in a function definition is rule 16.5.

MISRA C is still a far cry from Ada and SPARK, but it’s much better than coding without the use of a static-analysis tool. IAR provides sufficient customization to allow for additional checks without causing problems in development. It works best when using it on a new source code file. However, working it into existing code can be worthwhile as well.

Overall, I’m a fan of IAR Embedded Workbench, especially its MISRA C support. It has fewer bells and whistles than something like Eclipse, but that’s an advantage for many projects, especially if your focus is the micro.

If the IAR Embedded Workbench is your development platform of choice, then this kit is the ideal way to check out GigaDevice’s RISC-V microcontroller. You will be up and running in a day. The kit is also a useful way to evaluate the Workbench, which handles a wide range of processors including Arm, AVR, AVR32, STM8, MSP30, Renesas chip platforms, and the venerable 8051.