So...The Z80 is Rising from the Dead—with an On-Chip DAC?

What you’ll learn:

- The Z80 microprocessor was discontinued but VHDL instances survive.

- For less than $1,000, a chip like the Z80 can be taped out, including CAD tool cost.

- A complete Open-Source set of tools for doing a customized analog, digital, or mixed-signal design is available in a single download

Open-Source CAD tools

And multi-project foundries

Make chip design cheap

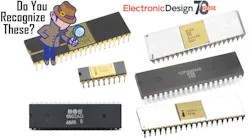

Birth and Death of the Z80

The first microprocessor was allegedly the 10-µm, 4-bit, Intel 4004, which was developed by Federico Faggin and available for purchase in November of 1971. A scant five months later, Intel introduced the 8-bit 8008, also fabricated on their 10-µm e-mode PMOS process on two-inch wafers. In 1974, the non-binary-compatible 8080, again developed under Faggin, came to market featuring much higher speed 6-µm NMOS technology.

That same year, Faggin would leave Intel to co-found Zilog, developing the company’s first product, the 5-V-only Z80 microprocessor that was backwards compatible with the 8080 instruction set.

The 5-µm NMOS Z80 was introduced in July 1976 and continued to be produced by Zilog for 48 years, with the company announcing the 4-µm Z80’s discontinuation on April 15, 2024.

Z80 Reincarnated

Less than a week after Z80’s discontinuation, and within a couple of days of hearing of the Z80’s demise, a veteran classmate of mine (more on that later), Renaldas Zioma, took it upon himself to prototype a Z80 in 130-nm CMOS. Most of the heavy lifting for the processor was already in place with a VHDL core already designed by Guy Hutchinson:

“TV80 is a Z80-compatible synthesizable Verilog core. The TV80 core aims to be an area-efficient core which closely mimics the original operation and cycle timing of the Zilog Z80. The core has been used by the author/porter in multiple silicon tapeouts as a utility processor or programmable state machine.” - Github

Renaldas’ target would be a multi-project wafer run in 130-nm CMOS, which would become open for new designs the following day and close for submissions six weeks later. The constraints of 29 pins, including power and ground, of the shuttle on the Z80’s 40 pins would mean that its 16-bit address and 8-bit control buses would need to be multiplexed as a 3-way interleaved 8-bit bus, which was implemented as a 4-way multiplexed interleave for simplicity. Not his first rodeo on the Open-Source CAD tools and process shuttle, Renaldas was the first tapeout on that August 2024 shuttle run. Now he waits for about nine months to have his baby on the bench.

Birth of a Cheap Chip

Back in mid-2017, DARPA (Defense Advanced Research Projects Agency) announced a program to increase innovation and provide innovators—startup companies and individuals[!]—with the ability to design and prototype full custom ASIC chips.

“The design portion of the initiative will focus on developing tools for rapidly designing and realizing specialized circuits. Unlike general-purpose circuitry, specialized electronics can be much faster and more energy efficient. Although DARPA has consistently invested in these application-specific integrated circuits (ASICs) for military use, ASICs can be costly and time-consuming to develop. New design tools and an open-source design paradigm could be transformative, enabling innovators to rapidly and cheaply create specialized circuits for a range of commercial applications.” - DARPA

Google, allegedly a big fan of Open Source (what corporation wouldn’t be a fan of free IP?), partnered with Skywater Technology to sponsor up to 100 projects on each multi-project wafer shuttle as part of the DARPA funding program. Startup eFabless provides the design framework of Open-Source tools, a standardized processor-based chip that handles probing and testing capability as well as selecting which user tiles of 512 get selected for power, ground, and I/O access.

“All projects created as part of the chipIgnite program will utilize a full chip reference design template that implements the physical IO for the chip as well as provides a common management area to support test and evaluation of the user’s design. The program also includes an optional automated open-source design flow for implementing projects that enables users to generate layouts for their digital projects from RTL. The chipIgnite program will provide users a guaranteed reservation to ensure their project is included.” - Skywater Press Release

At some point in time, Google seems to have dropped out of its benevolent free chips program, based on nothing new being published by researchers since 2022.

To add another layer of confusion, eFabless now offers Tiny Tapeout, which is service that includes a “Zero to ASIC” course on analog chip design, an easy-to-install Open-Source full chip design toolset, support on Discord, and biweekly calls that include the ability to ask questions from Harald Pretl, a professor at Johannes Kepler University. He’s been intimately involved in bringing up the standard cell libraries and additional analog capabilities. For under $1,000, Tiny Tapeout includes:

- Free design tools: Free access to design tools for implementing a project.

- Dedicated tile space: One tile offering 160 x 100 µm of area, and up to 1,000 standard cells.

- Fabrication and packaging: TinyTapeout takes care of fabricating and packaging the project into the Tiny Tapeout (“chipIgnite”) chip, turning designs into functional silicon. Submitting a design requires a Github account and sharing the now-Open-Sourced design on a public repository for everyone else to use, which is crucial to building more complex chip designs over time.

- Development board: A development board plus carrier board featuring your fabricated chip, which also includes all of up to 512 tiles of designs submitted.

- Digital datasheet and testing instructions: Gain insights with a digital copy of the datasheet that details each of the projects implemented on the chip and instructions on how to test them.

Z80 Gets an On-Chip DAC?

With the TinyTapeout philosophy of anyone being able to design a chip, and with the online class teaching chip design all the way from tools installation through tapeout and evaluation of a chip, I signed up for the beta version of the course. I did this primarily to be able to share this experience with our readers who may be interested in designing an obscure, discontinued, or original-design analog, digital, or mixed-signal chip.

“I've heard a lot about advances in processes for digital ICs and would be interested in hearing about what advances have been made in processes for analog IC's.” - Eric Magnuson, ED Reader comment on the day Z80 died

One of the turnoffs for Big Corp regarding offerings like Google Open Silicon and Tiny Tapeout is that any IP that’s instantiated is fully documented and licensed for subsequent reuse by a third-party participant in the program. For a limited resources startup, or an individual, though, it’s like having access to a full department of ASIC designers with zero cost for the tools to do a full chip design. Want to design a chip to control the speed of your HO-gauge loco? Now you can, versus rotting your retirement away in front of your 85-in. TV watching Futurama reruns.

Now in its eighth tapeout run (due Sept. 6), at least six prior runs’ worth of simulated, if not bench-tested, designs are available for reuse or instantiation into a larger design. Analog designs began trickling in with the fifth Tiny Tapeout, including such functional blocks as comparators, op amps, temperature sensors, SAR ADCs, DACs, etc.

Some of the interesting ones, out of hundreds of them, include:

- Analog Comparator

- DDS DAC

- Gilbert Mixer

- Simple FET Op Amp

- Instrumentation Amplifier for EKG

- 4-bit R2R DAC

- MOS Bandgap

- 1.8- to 5.4-V Dickson Charge Pump

- 12-bit SAR ADC

- AY-3-8913 Programmable Sound Generator

- 128x8 ROM

- 10-bit Moving Average Filter

- FIR Filter with Adaptable Coefficients

- 4-bit Flash ADC with Binary Encoder

- 10-MHz PWM Generator

- Over a dozen neuron projects on this tapeout

If one was inclined to do so, Renaldas’ Z80 could be easily bolted to one or more of these Open-Source designs using free Open-Source tools, creating, for example, a Frankensteined Z80 with three on-chip DACs for an application, such as generating an RGB display output. With 130-nm CMOS, a Z80 chip core would be severely pad limited, and it would take a couple of dozen cores to balance a fill to the padframe should an actual chip be eventually broken out. Imagine doing 256 cores of the Z80 on a chip...

What to Do?

Having signed up with Tiny Tapeout back in July, I have yet to install the CAD tools and watch the course materials due to the amount of work in this editor job that I’ve piled on for myself, let alone decide what to do for my chip design. With I/O bandwidth limitations of 75 MHz, it’s too slow for many of my aspirations, so I’m open to suggestions in the comments as to what may be interesting to do. I plan to provide updates here on Nonlinearities as I progress through the process. I’ll miss the September 6 tapeout, but a couple of others are coming up as well.

In any case, you, dear reader, can easily do a <75-MHz analog design for under $1,000...if you can find the time to do it, as money is no longer the problem. Then you need to think about what chip you’d like to do, which is the toughest part of this process—a standard building block or cell to contribute to this design revolution (likely what I’ll do), some discontinued oldie but goldie (Pong’s been sorta done), a chip that will compute Pi to a bazillion digits (1024’s been done), or perhaps an implantable empathy chip for billionaire warmongers’ brains like the one in Palmer Lucky’s skull.

All for now,

AndyT

Andy's Nonlinearities blog arrives the first and third Monday of every month. To make sure you don't miss the latest edition, subscribe to our Electronic Design Today newsletter.

About the Author

Andy Turudic

Technology Editor, Electronic Design

Andy Turudic is a Technology Editor for Electronic Design Magazine, primarily covering Analog and Mixed-Signal circuits and devices and also is Editor of ED's bi-weekly Automotive Electronics newsletter.

He holds a Bachelor's in EE from the University of Windsor (Ontario Canada) and has been involved in electronics, semiconductors, and gearhead stuff, for a bit over a half century. Andy also enjoys teaching his engineerlings at Portland Community College as a part-time professor in their EET program.

"AndyT" brings his multidisciplinary engineering experience from companies that include National Semiconductor (now Texas Instruments), Altera (Intel), Agere, Zarlink, TriQuint,(now Qorvo), SW Bell (managing a research team at Bellcore, Bell Labs and Rockwell Science Center), Bell-Northern Research, and Northern Telecom.

After hours, when he's not working on the latest invention to add to his portfolio of 16 issued US patents, or on his DARPA Challenge drone entry, he's lending advice and experience to the electric vehicle conversion community from his mountain lair in the Pacific Northwet[sic].

AndyT's engineering blog, "Nonlinearities," publishes the 1st and 3rd Tuesday of each month. Andy's OpEd may appear at other times, with fair warning given by the Vu meter pic.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: