Advanced technologies and constantly expanding application markets are moving the general design focus to systems on a chip (SOC). This has led to a heightened interest and importance in mixed-signal design-for-test (DFT) because the analog side of design is beginning to permeate digital development. And, when the speed goes as high as 90 GHz and soon probably more, even basic digital DFT must be re-examined in light of analog testing considerations.

Mixed-Signal DFT on the Rise

There is a common understanding that mixed-signal represents the interface between the real world and digital processing. Analog-to-digital (ADC) or digital-to-analog (DAC) converters are some examples. But that is not the only meaning of mixed-signal.

Otherwise, why are SPICE-like simulators developed for fully analog simulation used for digital cell design? Each time a critical performance is considered, such as delay, jitter, or rise and fall times, an analog simulation takes place.

The same is true with testing. Performance testing of digital cells is primarily an analog function. So together, digital and analog design and test form the mixed-signal environment.

The basic definition of DFT describes design efforts specifically used to ensure that a device is testable—whether that is analog, digital, or mixed-signal. This covers a broad spectrum of varying degrees of integration: from test access point insertion to full built-in self-test (BIST). After being overshadowed for years by digital DFT, mixed-signal DFT now is coming to the forefront thanks to the rise of SOC design and faster signals.

Just look at Silicon Germanium (SiGe) devices that exhibit speeds as high as 90 GHz. Digital-only DFT considerations are not enough for them. Since high performance is the driving force behind using such a technology, it is essential to include analog DFT.

Another example is precise jitter testing which is in demand now more than ever. In most cases, standard test equipment cannot deliver precision measurements. For now, only dedicated analog DFT solutions can. All of these trends point to one conclusion: mixed-signal DFT is a necessity and here to stay.

Interfaces Key to Viable DFT

What makes DFT really attractive for digital circuit developers is the capability to integrate it into the development process. This is especially true in standard digital design development, where interfaces now are available between the design environment—which includes DFT and test development—and the tester.

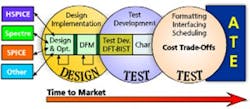

Figure 1 shows a typical scenario for a standard digital design flow that includes DFT and supports test development. As part of the design and test effort, automatic test pattern generation and fault simulation typically take place, if required. Moreover, scan and BIST insertion are becoming standard procedures as well.

Figure 1

Once all of the test information is generated within the design and test development environment, it must be ported to a particular tester. Traditionally, this porting requires that an interface be developed between the specific development tool and the specific tester. For digital circuits, there are several tools available that interface between different combinations of design tools and tester environments. This interfacing is critical for productivity, time-to-market, and efficient use of engineering resources.

Over the last couple of years, there have been extensive development efforts to automate this interface process. Not only have new interfaces to testers been developed with more comprehensive formatting, but also the tester programming language, Standard Test Interface Language (STIL), has been approved as a standard, with new interfacing products based on STIL on the way.

The purpose of STIL is to create a standard, automatic way to interface between any design environment and any tester. STIL resulted from ATE companies deciding to streamline the connectivity between test development and tester setup to improve productivity and time-to-market. But all of these efforts have been focused mainly on the digital side.

To become a mainstream capability, mixed-signal DFT requires the same level of interfacing to testers that has been developed for digital. The digital interfacing process took many years to develop, so it is impossible to expect immediate results for mixed-signal. But viable interfaces between mixed-signal DFT testers must be developed soon because they are needed to enable efficient, new, mixed-signal SOC development.

Figure 2 (see in the March 2000 issue) shows an integrated SOC development environment in general terms. Note that a potential BIST or DFT surrounds the device under test. Here, the DFT is a partial BIST with tester load board support, test probes, or other form of hardware-supported testability.

Other Considerations

Besides interfaces, other developments are necessary to promote mixed-signal SOC. One process step that is growing in importance is design-for-manufacturability (DFM), especially as IC fabrication processes continue to shrink. Yield analysis is becoming a major concern that must be included in a standard design and test methodology, especially mixed-signal SOC.

Another concern centers on expanding SOC functionality and the number of integrated modules. As more modules are included in an SOC design, the scheduling and cost trade-offs are being raised to a higher level of importance. With a different type of DFT for each module, which often is the case, the scheduling and management of the test process become major issues. Avoiding months of testing is a critical problem for SOC development.

Even traditional test-point insertion for digital testability requires a different implementation when dealing with extremely high-frequency digital signals. It needs to consider analog performance issues that result from high-frequency effects.

The traditional test point can degrade the performance of high-speed digital circuitry because of its capacitive loading. Instead, and to ensure optimal performance, a test probe designed not to disrupt the signal can be used. Since a test probe actually is a group of transistors, it can be developed and used as an intellectual property (IP) module.

Garnering More Attention

Although many issues still remain, solutions—full or partial—for mixed-signal DFT are on the way with more and more successful implementations in place. Last year, there was a major shift in how companies approached development methodologies. Today, more and more companies are considering analog and mixed-signal DFT as a critical missing part in the automated SOC development process. Consequently, more attention is being devoted to improving and incorporating existing mixed-signal DFT methodologies.

There also are techniques being developed for mixed-signal DFT including mixed-signal BIST. The most widely used and accepted are those that can easily win the cost-performance competition with legacy testing resources.

For SOC, these include phase-locked loop voltage-controlled oscillator (PLL-VCO) high-performance testing with picosecond jitter resolution. The appropriate BIST, like VCOBIST from Fluence Technology, is mostly integrated into IP but with additional output possibility for detailed result processing. The BIST circuitry does not require any integrated signal generator, so there is no calibration.

The internal VCO oscillations are used to observe the jitter and other characteristics depending on application. The necessary additional circuits are equivalent to about 2,000 gates and, by outputting the observed signals, detailed histogram analysis can be performed.

Other encouraging developments address new types of submicron fault models that are becoming much more common. In the past, a designer could make do with simple stuck-at-zero and stuck-at-one fault modeling using larger semiconductor geometries. However, as design moves into deep submicron, analog effects are beginning to have a major impact on digital performance.

For example, it is imperative that the impact of the interconnect on the SOC’s performance be modeled. With smaller gate sizes, the interconnect now plays a dominant role in the overall chip function. Consequently, it must be treated like an active component that can potentially introduce faults such as reflections, ringing, and crosstalk.

For the same reason, timing faults such as rise and fall times and delay must be carefully modeled. Faults also can stem from the fabrication process itself and should be addressed during testing. One such fault is bridging that can occur during fabrication. It can, for example, accidentally short two gates that should be independent of each other.

On Its Way

Mixed-signal DFT has come a long way in the past few years in response to emerging mixed-signal design types. But in addition to interfacing, this area still demands much more research and development for new DFT techniques and supporting tools. To successfully deal with all the issues surrounding mixed-signal DFT, a fully integrated development environment is becoming essential for SOC designs.

Analog designers and DFT engineers often are slow in accepting full analog test integration, which is quite understandable. Very often, the transition of choice is a combined analog and digital solution because it has minimum impact on a design and maximum impact on the tester load board. This is a practical transition that helps build confidence when moving toward a true analog/mixed-signal DFT.

Although there still remains a considerable amount of work to be done, the recent increase in attention to mixed-signal DFT needs is very encouraging. It is creating a strong move toward resolving the challenges of this demanding, yet exciting, technology.

About the Author

Dr. Bozena Kaminska is the senior vice president and chief technical officer at Fluence Technology. Dr. Kaminska co-founded Opmaxx, the first mixed-signal DFT company that now is merged with Fluence. Before starting Opmaxx, she was affiliated with the University of Montreal as a professor in the Electrical Engineering Department. She earned a Ph.D. in microelectronics at Warsaw Technical University in Poland, authored or co-authored more than 100 papers, and holds several patents. She also is a member of the IEEE and chair of the IEEE Test Technology Technical Committee on Mixed-Signal Testing. Fluence Technology, 8700 SW Creekside Place, Beaverton, OR 97008, (503) 672-8800.

Return to EE Home Page

Published by EE-Evaluation Engineering

All contents © 2000 Nelson Publishing Inc.

No reprint, distribution, or reuse in any medium is permitted

without the express written consent of the publisher.

March 2000