DSP-Based Radar, LiDAR, Comms Processing Optimizes Auto Apps

This article is part of TechXchange: LiDAR Technology

What you'll learn:

- The key design features driving the new Tensilica ConnX DSPs.

- What capabilities do the DSPs offer?

- Language and library support.

Today’s automobiles incorporate dozens of embedded processors connected via multiple digital networks, controlling and enhancing the operation of nearly every system. But whether the target is vehicle-to-vehicle, vehicle-to-infrastructure, 5G communications, a high-resolution imaging radar sensor, or a lower-cost solid-state LiDAR, all can benefit from the flexibility of a software-based solution. This flexibility can best be achieved by implementing parts of the signal-processing chain using programmable processors.

The new Tensilica ConnX 110 and ConnX 120 digital signal processors (DSPs) developed by Cadence aim to offer engineers the needed flexibility and performance for radar, LiDAR, and communications applications. They can include legacy support for 4G, LTE Advanced, LTE, WCDMA, HSPA+, Wi-Fi, and DVB.

“Radar and communications processing trends require solutions that perform more processing in less time,” said David Glasco, vice president of research and development for Tensilica IP at Cadence. “Automotive radar demands multi-antenna, high-resolution systems with rapid response.

“Similarly, 5G wireless communications requires much higher data rates and lower latencies than previous generations. The Tensilica ConnX 110 and ConnX 120 DSPs meet these demands by extending the already-efficient processing capability of the ConnX DSPs and enhancing them with even more fixed- and floating-point complex data-processing capacity at low power and area.”

DSP Details

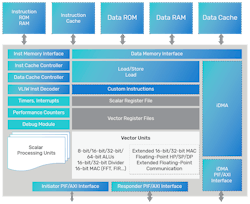

The ConnX DSPs do so via highly parallel vector engines and, with compatible architectures, provide an upgrade path to other ConnX family members when needed. Similarly, if processing needs scale beyond that of a single DSP, the ConnX family can provide support for multicore solutions.

As needed, hardware blocks may be interfaced to the Tensilica ConnX processors via dedicated custom interfaces under the ConnX processor control or as initiator/responders via the system bus interfaces or via shared memory.

The ConnX processors, well-suited for running control code, are used to perform the PHY application-layer control in addition to digital signal processing. This opens the door to opportunities for hardware savings and a broader scope of applications than a dedicated fixed hardware solution is likely to provide.

The Tensilica ConnX DSPs offer pre-verified accelerator instruction options. These options are included/excluded as checkboxes when defining a core, resulting in efficient integration of that feature into the hardware, the compiler, the modeling tools, and the verification scripts. With these capabilities, designers can build a custom DSP without the large development schedule impact that would normally be involved with a change in hardware design.

The 128-bit ConnX 110 DSP and 256-bit ConnX 120 DSP feature an N-way programming model and are fully compatible with the higher-performance ConnX B10 and B20 DSPs, sharing a common instruction set architecture for easy migration.

N-version programming, also known as multiversion programming, is a method or process in software engineering where multiple functionally equivalent programs are independently generated from the same initial specifications. The aim is to improve the reliability of software operation by building in fault tolerance or redundancy.

Tied into TIE

Like the rest of the Tensilica DSP portfolio, the ConnX 110 and ConnX 120 support the Tensilica Instruction Extension (TIE) language. TIE allows users to tailor the instruction set, add specialized data types, and implement integrated interfaces between the DSP and external logic. In addition, the new DSPs are supported by a comprehensive set of complex math library functions in the NatureDSP, Eigen, and Radar libraries. All ConnX DSPs are automotive-ready with full ISO 26262 compliance to ASIL-D with FlexLock or to ASIL-B.

The Tensilica ConnX 110 and 120 DSPs offer the following features and capabilities:

- Optimized instruction set for radar, LiDAR, and communications applications.

- Fast development through familiar C programming in an Eclipse-based IDE along with optimized math libraries and application examples with source.

- 128-bit (ConnX 110) and 256-bit (ConnX 120) SIMD performance for complex math operations based on 8-, 16- and 32-bit fixed-point, and half-, standard- and double-precision floating-point.

- A common instruction set and simplified programming model, allowing code to be written once and utilized across different SIMD widths within the ConnX family.

- Architecture optimized for a small memory footprint and low-power signal processing.

- Optional acceleration operations for linear-feedback shift, convolutional encoding (a type of error-correcting code), single peak search, and dual peak search

- The ConnX 120 also offers Viterbi and Turbo decoders.

The Tensilica ConnX DSPs are delivered with a complete set of software tools. The toolset includes a C/C++ compiler with automatic vectorization and instruction bundling to support the VLIW pipeline in the DSP. In addition, the toolset includes the linker, assembler, debugger, profiler, and graphical visualization. An instruction set simulator (ISS) allows users to quickly simulate and evaluate performance.

When working with large systems or lengthy test vectors, the TurboXim simulator option achieves speeds that are said to be 40X to 80X faster for efficient software development and functional verification. Xtensa SystemC (XTSC) and C-based Xtensa Modeling Protocol (XTMP) system modeling are available for full-chip simulations. Pin-level XTSC provides co-simulation of SystemC and RTL-level offload accelerator blocks for fast, cycle-accurate simulations.

Read more articles in TechXchange: LiDAR Technology