Linear Monostable Converts Capacitive Transducer Measurements into Pulse Train

Members can download this article in PDF format.

What you'll learn:

- How to build a circuit that converts capacitance into a pulse train.

- Test results of the circuit design.

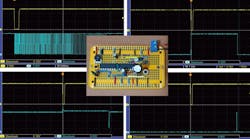

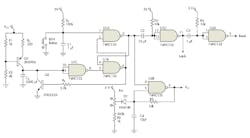

The circuit in Figure 1 allows you to convert capacitance into a pulse train by using a constant current source and a linear monostable formed by two NAND-gate chips (74HC132). The circuit also provides two pulses to control external counter functions such as Latch and Reset, which are normally required by digital counters and latches when driving a display. Applications for the monostable include instrumentation circuits when the need arises to convert a transducer’s capacitance measurement (such as relative humidity), into a pulse train.

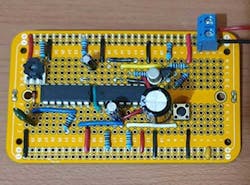

CX represents the capacitance transducer (Fig. 1, again). The circuit is triggered by a N.O. pushbutton, which has a debouncing network formed by RP and C1 to create a clean transient Low pulse. Figure 2 shows the actual assembled circuit on a printed circuit board (PCB). A 0.1-µF bypass capacitor is placed between voltage and ground.

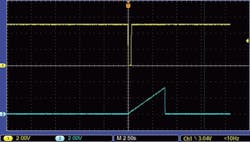

In its initial state, U1B is high, driving transistor Q2 in saturation, which keeps capacitor CX grounded (Fig. 3). This disables the gated oscillator formed by U2B.

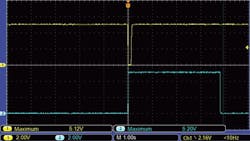

When the pushbutton is pressed, the SR latch makes U2A go high while U21 goes low (Fig. 4). This puts transistor Q2 in cutoff, allowing CX to charge linearly with a constant current.

The constant current source is formed by Q1, a PNP transistor, and its associated components. This constant current IK is defined by Equation 1:

IK = (VCC – Vb – Vbe)/RE (1)

where VCC = 5.1 V, Vb = 4.1 V, and Vbe = 0.7 V. To get the timing constant T, we substitute the current IK in variable R as follows in Equation 2:

T = R CX = (VCCCX)/IK (2)

Equation 2 is then multiplied by the ratio (Vt+/VCC), which is defined by the positive threshold voltage in NAND gate U1C and VCC. This ratio represents the maximum voltage that capacitor CX will reach. By substituting IK in Equation 2, we get a linear timing and charging ramp (Fig. 5) with its respective Equation 3:

T = [(VCC)CX × (VCMAX/VCC) × RE]/(VDD – Vb – Vbe) (3)

Then we substitute our component values and voltage measurements to get Equation 4:

T = [(5.12 V)(2200 µF)(3.28 V/5.12 V)(220 Ω)]/(5.12 V – 4.08 V – 0.636 V) (4)

When capacitor CX = 2200 µF is placed, for example, we get a time period equal to 3.9 seconds. The accuracy of this result depends on the tolerance of all the components contained in Equation 4.

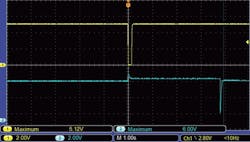

The constant current IK stops charging capacitor CX when its voltage reaches the positive threshold voltage Vt+, in this case 3.28 V. At this point, NAND gate output U1C goes to a logic low, disabling the oscillator, and generates two transient pulses in sequence with the half-monostables formed by NAND gates U1D and U2A.

The edge detector formed by U1D is triggered at the falling edge (Fig. 6) from the output pulse coming from NAND gate U1A.

The positive transient pulse produced by NAND gate U1A is called Latch (Fig. 7), and its period T2 is given by Equation 5:

T2 = R3C2Ln[VCC/(VCC – Vt+)] (5)

When this pulse ends, it triggers the second half-monostable formed by R4 and C3, producing a positive transient Reset pulse T3 (Fig. 7, again) defined by Equation 6.

T3 = R4C3Ln[VCC/(VCC – Vt+)] (6)

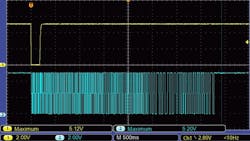

The gated logic oscillator formed by NAND-gate U2B and its associated components delivers a pulse train (Fig. 8) at a frequency defined by Equation 7:

F = {1/R5C4Ln[(Vt+/Vt−) × (VCC − Vt−)/(VCC – Vt+)]} (7)

This oscillator doesn’t have a startup delay because the 500k trimpot in series with R6 must be calibrated a few millivolts below the positive threshold voltage Vt+ (see the reference below). Notice that when this oscillator is disabled, capacitor C5 requires a time delay to again reach the fixed voltage set by the trimpot. This time delay may vary depending on the capacitor’s voltage before it was disabled. If the capacitor’s voltage was equal to Vt− when it was disabled, it will require a recovery time defined by Equation 8:

T2 = R5C4Ln [(VCC − Vt−)/(VCC – Vt+)] (8)

This delay sets the time you must wait to apply the next pulse on the pushbutton. The oscillator frequency is set with a fixed capacitor C4 and resistor R5 according to the counter resolution and desired precision reading. You can add a series potentiometer to R5 to adjust such a frequency.

This circuit can be made to retrigger by itself. A feedback loop would be placed from the Reset Pulse to the pushbutton input, using another edge detector triggered at the falling edge. This would require the edge detector to provide a Low pulse on the trigger input with a minimum period equal to 1 µs. RP would not be required. Bear in mind that when triggered by itself, the external counter will keep changing its readings continuously at a rate given by Equation 3. A display must update its readings within one to four times per second; otherwise, it will appear as flickering.

It’s recommended to use 1% tolerance metal film resistors to get variations of up to 1% due to changes in temperature. With respect to the capacitors, you must use polyester or polystyrene types to have minimum value changes with respect to temperature. In addition, the trimpot for R5 must have a low temperature-coefficient constant.

Reference

“Gated Oscillator Starts Without Delay,” Electronic Design.