Staying Current: Midyear 2025 EDA Tools for Engineers (Part 2)

What you'll learn:

- The latest in EDA tools across different practices.

- Who is leading in EDA tools?

- Where to begin with EDA tools.

I felt the list of the best of the latest in EDA tools needed to be broken up into two parts. There are so many that we all should be familiar with, and these roundups offer a perfect launching off point.

Real Intent Ascent AutoFormal

Real Intent’s Ascent AutoFormal is a formal linting tool designed for automatic and early verification of register transfer level (RTL) code in digital designs. The platform builds on the company’s Ascent Lint technology by incorporating deep-sequential formal analysis to identify sequential bugs that could be overlooked during traditional simulation tests. These include finite-state-machine (FSM) deadlocks, unreachable states, range violations, constant nets, dead code, and more.

Ascent AutoFormal provides support for designs with millions of gates, offering over 10X speed-up compared to previous versions. It also provides root cause analytics, integrated debugging tools, and parallel processing support.

SynaptiCAD WaveFormer Pro

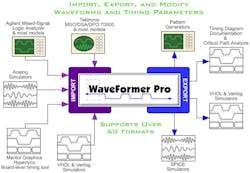

WaveFormer Pro is a rapid prototyping EDA tool that integrates a timing diagram editor, a stimulus generator, and an interactive hardware description language (HDL) simulator.

Developed by SynaptiCAD, the platform allows engineers to automatically generate, simulate, and analyze timing diagrams using common Boolean and registered logic equations without the need for schematics or simulation models. It can also import or export waveforms to VHDL, Verilog, Tektronix, HP, and Agilent logic analyzers, pattern generators, SPICE, ABEL, and a host of gate-level simulators.

Agile Analog Composa

Agile Analog’s Composa is designed to automate the creation of customizable and process-agnostic analog IP solutions for system-on-chip (SoC) and application-specific integrated-circuit (ASIC) development. The platform integrates major foundries’ (Intel, Samsung, SMIC, TSMC, etc.) process development kits (PDKs), which provide automatic regeneration of analog IP to suit different foundries or process nodes without the need for re-engineering.

Composa enables engineers to specify requirements such as power consumption, area, speed, and accuracy, then utilizes a library of validated analog circuits to generate optimized IP tailored to their specifications. The platform’s automated generation and optimization capabilities help reduce the time to develop and integrate analog IP from months to weeks.

Siemens Questa One

Questa One from Siemens EDA is an AI-based smart verification platform targeted for IC and SoC designs, including those with 3DIC and chiplet-based architectures. The platform leverages AI and ML to automate workflows, accelerate verification, and enhance coverage by bridging productivity gaps in complex designs.

Questa One increases performance and productivity with faster simulation engines and automated workflows, and provides access to Siemens’ EDA ecosystem. Along with Questa One, this involves the Tessent DFT and Veloce CS emulation and prototyping systems.

Additional features include using generative AI to auto-generate assertions, test plans, and similar artifacts; utilizing predictive modeling to prioritize regression tests and improve coverage closure; and providing predictive failure analysis, root-cause identification, and commit-based debugging.

Cadence Jasper Formal Verification Platform

Cadence’s Jasper Formal Verification Platform combines high-performance formal engines with intuitive debug capabilities that help engineers validate hardware designs at the C/C++ and RTL levels.

The platform is an all-in-one solution that takes advantage of ML to verify hardware designs using formal methods. Its core function is to find and eliminate bugs early in the design cycle, utilizing Cadence’s Jasper Visualize Interactive Debug Environment with QuietTrace, which increases verification efficiency and productivity.

The Jasper Formal Verification Platform provides access to Cadence’s app-specific ecosystem for verification applications, including the Jasper Formal Property Verification (FPV), Jasper C, Jasper Sequential Equivalence Checking (SEC), Jasper Security Path Verification (SPV), Jasper Connectivity Verification, and Jasper Design Coverage Verification (COV).

Siemens Calibre Physical Verification nmPlatform

Calibre Physical Verification nmPlatform is Siemens’ EDA solution for integrated-circuit (IC) design. The platform features a comprehensive suite of tools for various stages of IC development, from design verification to manufacturing. The platform’s core engines cover DRC, LVS, PEX, and reliability verification, ensuring compliance with foundry rules, schematic-to-layout consistency, and accurate modeling for signoff-quality simulations.

Calibre includes tools such as nmDRC, which offers high-capacity, high-performance rule checking, and nmLVS, providing device and connectivity extraction. Calibre nmDRC Recon enables early-stage DRC on partial layouts to reduce late-cycle debug, and Calibre Auto-Waivers automates waiver tracking for approved violations. It also incorporates Calibre Pattern Matching, Calibre Multi-Patterning, Calibre 3DSTACK, and the Calibre DFM suite. These offer litho simulation, yield analysis, and printability checks.

Conclusion

EDA in 2025 isn’t just about simulation speed or timing closure. It’s also about building efficient, optimized designs with fewer bugs and increased predictability. The tools listed here are just a few of the platforms engineers can utilize to handle bigger chips, tighter nodes, and shorter schedules without signing off on quality. With that said, dig into the capabilities, and you’ll see why these platforms are redefining how silicon gets designed and verified today.

About the Author

Cabe Atwell

Technology Editor, Electronic Design

Cabe is a Technology Editor for Electronic Design.

Engineer, Machinist, Maker, Writer. A graduate Electrical Engineer actively plying his expertise in the industry and at his company, Gunhead. When not designing/building, he creates a steady torrent of projects and content in the media world. Many of his projects and articles are online at element14 & SolidSmack, industry-focused work at EETimes & EDN, and offbeat articles at Make Magazine. Currently, you can find him hosting webinars and contributing to Electronic Design and Machine Design.

Cabe is an electrical engineer, design consultant and author with 25 years’ experience. His most recent book is “Essential 555 IC: Design, Configure, and Create Clever Circuits”

Cabe writes the Engineering on Friday blog on Electronic Design.