Frequency Quadrupler Enables Low-Frequency Measurements, Spans Up To Four Decades

This article is part of the Ideas for Design Series: Vol. 3, No. 2

In frequency counters, the gating time allotted for counting is often too short to resolve low frequencies. A phase-locked loop could be used to multiply the input frequency. But in some cases, the signal changes too fast or too far for lock to be acquired or maintained.

Related Articles

- RS-232 Port Powers Frequency Counter

- Counter Circuit Improves Oscilloscope Triggering

- Tachometer Measures Very Low Frequencies

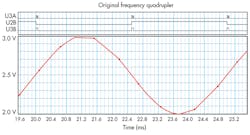

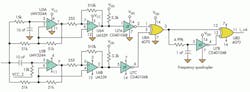

To solve the problem, the circuit of Figure 1 is used to multiply the input frequency by a factor of four, spanning a range of 1 Hz to over 40 kHz, and it will track a step change anywhere in that range.

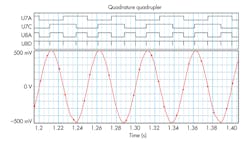

Figure 4 shows the benefits provided by the quadrature circuit. The first XOR gate, U8A, produces the exclusive OR of the two quadrature outputs, U7A and U7C. This multiplies the input frequency by two. The second XOR gate, U8D, produces a pulse for each positive and negative edge of the signal from U8A, again multiplying by two. The result is four equally spaced output pulses at U8D for each cycle at the input.

Accurate tracking speed may be limited by the time required to acquire four output pulses at the new frequency from a step change to an accurate count, effectively a delay of 1/f seconds. This implies that accurate tracking is a function of the input frequency. Stepping from a higher to a lower frequency would require at least 1/flower seconds for the output to settle at four times the input frequency.

The output pulse is set wide enough to be reliably captured by the processor or other counter input. If it is too wide, it will limit the upper frequency at which multiplication can be achieved. Too narrow, and the microprocessor or counter will miss counts.

With the components shown, the output is a 5.6-μs pulse. This restricts the maximum theoretical multiplied output frequency to 89.3 kHz (input frequency less than or equal to 22.3 kHz). The quadrature circuit component values limit the maximum input frequency to 49 kHz or 196 kHz at the output of the multiplier. If the output pulse width could be made as short as 2.5 μs, the maximum multiplied output frequency would reach 196 kHz.

Adjusting component values can move the usable range of multiplication higher or lower than that described here to fit the user’s requirements. With faster op amps, comparators, and logic components, the design might be able to perform at RF frequencies.

Read more articles from the Ideas for Design Series: Vol. 3, No. 2

This file type includes high resolution graphics and schematics when applicable.

Dave Conrad is a retired analog/digital hardware engineer who learned electronics by reading (starting at age 6) publications such as the ARRL Radio Handbook, QST, and CQ and later from various library books and Popular Electronics magazine. This was followed by a few courses in electronics in high school and junior colleges including TTL logic, along with learning on the job.

About the Author

David Conrad

Retired Analog/Digital Hardware Engineer

Dave Conrad is a retired analog/digital hardware engineer who learned electronics by reading (starting at age 6) publications such as the ARRL Radio Handbook, QST, and CQ and later from various library books and Popular Electronics magazine. This was followed by a few courses in electronics in high school and junior colleges including TTL logic, along with learning on the job.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: