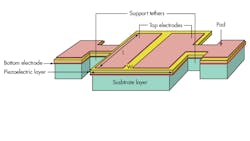

Silicon Labs’ process starts with standard, passivated, and planarized CMOS wafers. Polycrystalline silicon-germanium (Poly-SiGe) and pure germanium (Ge) are surface micro-machined to create integrated MEMS devices on top of the CMOS circuitry.

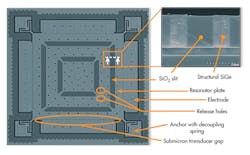

Silicon Labs isn’t saying precisely how its process technology can create microstructures without destroying the underlying CMOS IC. But the company will show photos of the resonator structure (Fig. 1). What one sees is a square plate with slits of silicon dioxide. Those slits are a key component of Silicon Labs’ intellectual property. The company says the technique avoids the temperature sensitivity of other companies’ processes.

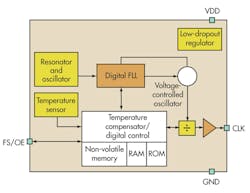

Silicon Labs says this comes about because the CMEMS resonator is fabricated from both polymorphous SiGe and silicon dioxide (SiO2). The temperature coefficient of the SiO2 compensates for the temperature coefficient of the SiGe, and the resulting resonator temperature coefficient is in single-digit ppms/°C. As with any semiconductor clock, these MEMS oscillators use this passively compensated resonator for a reference frequency with which to drive a cost-optimized, power-efficient digital frequency-locked loop (FLL) (Fig. 2).

The FLL uses the MEMS reference frequency along with a divided signal from an on-chip voltage-controlled oscillator to drive a frequency comparator that generates frequency error values and feeds them to the FLL’s digital loop filter. The FLL also handles temperature compensation, using an on-chip sensor. For more, see “CMEMS Oscillator Architecture.”

About the Author

Don Tuite

Don Tuite (retired) writes about Analog and Power issues for Electronic Design’s magazine and website. He has a BSEE and an M.S in Technical Communication, and has worked for companies in aerospace, broadcasting, test equipment, semiconductors, publishing, and media relations, focusing on developing insights that link technology, business, and communications. Don is also a ham radio operator (NR7X), private pilot, and motorcycle rider, and he’s not half bad on the 5-string banjo.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: