Dual-Core SoC Utilizes FD-SOI for Low Power and High Performance

Download the PDF of this article.

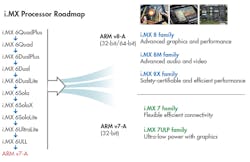

Designers are employing a range of techniques, like Ambiq Micro’s subthreshold designs to reduce power consumption while delivering high performance devices. NXP is employing 28-nm FD-SOI (28FDS) technology with its new i.MX 7ULP family, targeting applications ranging from wearables to automotive. The i.MX 7ULP family is the low power migration path (Fig. 1) from the popular i.MX6 family.

1. NXP’s 28-nm FD-SOI technology is used to build the i.MX 7ULP family that replaces the low end of the popular i.MX6 family.

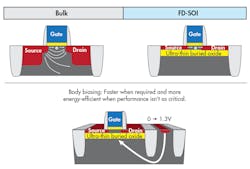

FD-SOI utilizes an ultra-thin buried oxide layer (Fig. 2) to improve electrostatics, thereby enabling shorter gate lengths. It also makes the gates immune to latch up. The approach provides a 10× to 100× improvement in soft error rate (SER) performance.

FD-SOI also helps in reducing device parasitics, and the use of device back bias allows performance to be maintained while lowering VDD. There is improved analog peripheral performance with higher gain, better matching, and lower 1/f noise enhancements. The gate-first integration removes density rules for precision analog. Device tuning with back biasing is employed to compensate for process variation.

2. FD-SOI utilizes an ultra-thin buried oxide layer.

NXP developers used domain and subsystem optimizations to design the chips, along with a custom standard cell library with mixed voltages. They employed a large dynamic gate and body biasing voltage (VBB) range to address speed and power requirement tradeoffs and to deliver an extreme low leakage implementation.

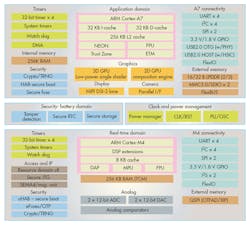

The system actually use a dual-core, asymmetric design with an ARM Cortex-A7 paired with an ARM Cortex-M4 (Fig. 3). The cores can operate independently when it comes to operation and sleep mode. Versions of the i.MX 7ULP are available with the 3D Vivante GC7000 NanoUltra 3D GPU with a low-power single shader, or the GC320 Composition Processing Core (CPC) for 2D graphics support.

3. The i.MX 7ULP uses a dual core, asymmetric design with an ARM Cortex-A7 paired with an ARM Cortex-M4.

The chip has secure boot support for both cores and the QPSI interface supports on-the-fly encryption and eXecute-in-place (XIP) support. The Cortex-M4 has access to the typical serial and digital peripherals as well as a set of dual-channel 12-bit ADCs and DACs. The Cortex-A7 sports USB 2.0 host and OTG interfaces. The TrustZone hardware support includes a true random number generator (RNG), as well as crypto hardware with AES-128/256 support and secure fuses for unique identification, plus secure storage. The system has tamper detection support and a secure real-time clock (RTC).

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: