Dual-Issue Multicore SOC Handles Soft Peripherals

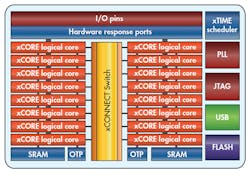

More and more multicore solutions are now targeting embedded applications, but XMOS has been pushing hard, real-time, multicore solutions for quite some time. The latest xCORE-200 platform has up to 32 lightweight, 32-bit cores and a 1-Gbit Ethernet interface (Fig. 1). The family has up to 2 Mbytes of flash and 1 Mbyte of SRAM and does 64-bit transfers. XMOS developers take a different approach to real-time parallel processing; cores are designed to wait for events instead of using interrupt routines that have latency and overhead issues.

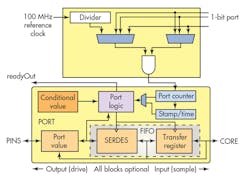

The xCORE-200 uses a dual-issue instruction decode providing improved performance compared to the original xCORE series. Each core can run applications like a conventional microcontroller, but they are also designed to be dedicated to an activity (such as handling high-speed communication). The hardware response ports allow very efficient bit-banging, soft peripheral solutions (Fig. 2). They can be configured from 1- to 32-bits.

A core can stop and wait for an event so there is no interrupt overhead. The large number of cores allows numerous interfaces to be supported by a single chip. A full duplex serial can be implemented using a core to transmit and receive, and another to coordinate these functions. It is also possible to run multiple tasks on a core supported by a hardware scheduler that can handle core and task priorities. This programming approach can actually be easier compared to interrupt handlers, especially when timing considerations are taken into account.

The xCONNECT switch provides communication between cores. Some xCORE-200 chips allow these switches to be interconnected. Cores can communicate with each other regardless of where they are located. The switch is also deterministic. This capability is significant when combined with the soft peripherals and deterministic memory access.

The chips are built around tiles that have multiple cores. Each tile has local SRAM and one has flash memory attached to it. Each tile also has OTP memory to support secure boot and encryption keys.

Developers can check out the new chips using the xCORE-200 eXplorer Kit (Fig. 3), which has a 2000 MIPS, 16-core XE216-512 chip with 512 Kbytes of SRAM, 6 servo interfaces and a 1 Gbit Ethernet port. It has a High-Speed USB interface in addition to a 3D accelerometer and magnetometer.

XMOS provides xTIMEcomposer Studio, an Eclipse-based IDE, that includes fully standards-compliant C and C++ compilers. There is additional support for XMOS parallel processing and communication services, but this is similar to the runtime support for any microcontroller.

About the Author

William Wong Blog

Senior Content Director

Bill's latest articles are listed on this author page, William G. Wong.

The latest blogs have been moved to alt.embedded on Electronic Design.

Bill Wong covers Digital, Embedded, Systems and Software topics at Electronic Design. He writes a number of columns, including Lab Bench and alt.embedded, plus Bill's Workbench hands-on column. Bill is a Georgia Tech alumni with a B.S in Electrical Engineering and a master's degree in computer science for Rutgers, The State University of New Jersey.

He has written a dozen books and was the first Director of PC Labs at PC Magazine. He has worked in the computer and publication industry for almost 40 years and has been with Electronic Design since 2000. He helps run the Mercer Science and Engineering Fair in Mercer County, NJ.

- Check out more articles by Bill Wong on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: