This file type includes high resolution graphics and schematics.

IC physical verification (i.e., design rule checking or “DRC”) used to be easy. In the good old days, you could run some one-dimensional (1D) width and spacing checks to ensure things would not short, and you would be good to go. These checks were simple to write, fast to run, easily understandable, and quick to debug. But with today’s deep sub-resolution lithography, these attributes are no longer enough.

Related Articles

- Calibre Pattern Matching: Picture It, Match It, Done!

- Programmed Splitting Of Full-Chip Calibre DRC/ERC Errors Into Sub-Block Space

- What Does Design Rule Signoff Really Mean, And When Should I Care?

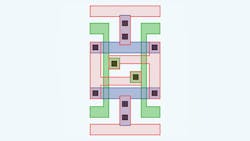

More and more checks are two-dimensional (2D), very complex to write, and tough to code so they run fast. They’re also increasingly difficult to debug. Trying to describe these complex 2D checks using syntax originally designed for 1D checks has caused design rule implementations to balloon. Fortunately, a new approach called pattern matching (PM) addresses these and other challenges, and it is making significant inroads into mainstream physical verification (PV). PM enables designers to go from a dirty design to tape-out in much less time, and with less effort, than would otherwise be possible (Fig. 1).

What’s The Problem?

Moore’s law has moved ahead of the IC lithography industry’s resolution improvements, so EDA software now must provide a larger fraction of the resolution enhancement. As ICs shrink, the range over which lithographic and electromechanical interactions occur expands relative to the size of individual physical features or cell sizes (Fig. 2). In addition, with wafer steppers using 193-nm light sources, the distortions due to diffraction effects result in more numerous and subtle context-dependent design-for-manufacturing (DFM) issues.

To compensate for these complexities, design rules have to be much more complex to ensure that a layout does not have features (shapes) that cannot be accurately manufactured. From simple 1D spacing, length and width measurements between immediately adjacent features such as transistors or interconnect wires, IC design rules have evolved to account for many more complex 2D geometric measurements. In addition, it is often necessary to consider a group of measurements related by complex functions to determine if a feature can be manufactured at advanced process nodes.

Trying to elegantly express these complex design rules in a linear, textual language can be extremely difficult, which translates to more time spent implementing design rules in the PV tool and more time debugging the rules. An alternate approach is to express these complex design rules directly as layout patterns, either allowable patterns or forbidden patterns, and have the PV tool search for them in the layout being checked.

When a layout feature “matches” a forbidden pattern, it can be marked or processed to aid in human comprehension and debugging. The design rule patterns can be built up from experience during process development, through analysis of test chips, and through failure analysis of failed chips. Many patterns can be carried forward from one node to the next with suitable adjustments. Not only are patterns an easier way to express complex 2D relationships, they also provide a directly useful way for design and manufacturing engineers to communicate design for manufacturing (DFM) issues.

Addressing Yield Detractors

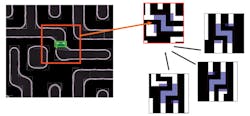

Given all these advantages, PM has become a major component in a variety of operations associated with PV and DFM. One of PM’s most useful applications is to remove yield detractors that have been identified by the foundry (or fab). A yield detractor pattern is a shape (or a group of shapes) in the design layout that has been shown to be a systematic (non-random) source of chip failures (Fig. 3). Yield detractor patterns result from many manufacturing issues including lithography and etching characteristics. At 28 nm and below, many leading foundries provide yield detractor decks in the form of forbidden patterns to their customers. Like DRC, checking to ensure that none of these patterns are present in the layout is a mandatory step to complete tape-out signoff.

This file type includes high resolution graphics and schematics.

In parallel with the growing use of yield detractor pattern libraries by the foundries, fabless companies have been using more pattern matching. Within their own failure analysis organizations, fabless companies identify yield detractor patterns based on issues from prior designs. Application of this knowledge is sometimes driven by a joint quality process with their foundry and sometimes by the fabless company’s own unique design methodologies.

In either case, the yield detractor pattern libraries are used to identify weak (or “suspect”) patterns in the designs that are in progress. These patterns then are removed before the design is completed. When fabless companies do this internally and maintain the growing pattern library as proprietary information, they can create a real competitive differentiator for themselves. They are potentially able to avoid re-spins, ramp to volume faster, and reduce design variability for their unique design styles.

Streamlined Failure Analysis

With traditional approaches, the amount of time it takes to provide actionable information back to a design team once the failure analysis (FA) engineer finds a systematic error in a scanning electron microscope (SEM) or tunneling electron microscope (TEM) can be measured in weeks or months. That’s way too slow for today’s consumer markets.

The typical approach is for the FA engineer to capture SEM/TEM images, draw examples of the offending geometries, and try to write a specification for a new design rule to prevent the yield detractor pattern from being allowed in a design. The new rule is then passed on to a different person who needs to interpret the rule and write a new DRC check using only text-based, PV scripting language. The challenge is to quickly, yet accurately, describe the original pattern, and all of its variants, and then to associate a design rule with it. The parameters of the design rule depend on a lot of factors, including how prevalent the pattern will be in future designs. This is all a manual effort and proceeds seemingly at glacial speeds.

In contrast, with a PM approach an FA engineer can clip out a yield detractor pattern from a design exhibiting the failure and directly include it in a library of suspect patterns that can be used to check both the failing design (to validate a strong correlation between this pattern and failures in the design) and all future designs or designs in progress. Essentially, the PM methodology increases the level of automation and provides faster feedback to the designers of the next designs. What’s not to like?

Productivity (Filtering)

With the enormous number of polygons to be analyzed in designs today, some types of computationally intensive modeling or analysis such as full-chip lithography simulation at the full chip level without filtering down the incoming data have become impractical. Most major foundries require full litho simulation at the cell and block level with a combination of pattern matching and litho simulation at the full chip level for designs targeting advanced processes. Pattern matching is used as a filter to identify areas that are potentially litho hotspots. Simulation is then run on these areas to determine if the potential hotspot is truly a hotspot in the context providing an overall solution with acceptable run times while also maintaining a very high level of confidence in the results.

Design Accuracy, Methodology

One of the growing areas of interest is the use of pattern matching to help reinforce a company-specific design methodology. For example, some companies use pattern matching to verify that certain cells or devices are drawn one way and one way only. This type of design methodology checking is very challenging to perform with only traditional DRC approaches.

On the other hand, it is easy to capture “best practice” design patterns from the “super users” and make them part of the company’s overall DRC decks that all designers must run on their designs. In addition to specific design styles that the fabless companies may have, most foundries also have an ever growing list of test patterns, fill cells for the end of tracks, and other required or recommended patterns that must be used consistently by the designers. Again, this is challenging to implement with only traditional approaches.

A related methodology is to complement “restrictive design” with “proscriptive design.” Traditional PV is based on identifying design constructs that must be avoided. Proscriptive design turns this around by requiring designers to build layouts exclusively from known good design elements (i.e., patterns) and then perform PV with a library of these acceptable patterns. Any patterns introduced other than the approved ones are regarded as errors.

Sounds great, right? Sure, if you’re a foundry or fab person responsible for manufacturing the design. But if you’re a designer, it feels like all your design freedom has been taken away. Even the words “restricted design rules” bring to mind reduced freedom rather than an understanding that some patterns are difficult to manufacture. This is the state of the debate today. Maybe at 7 nm we’ll be forced to employ more proscriptive design. Only time will tell.

Important Tooling Considerations

What are some of the features you want to see in a design flow that takes advantage of PM technology? One big consideration is whether the PM features work seamlessly with traditional design rule approaches. There are many reasons why you will not replace your entire DRC rule deck with patterns—some rules don’t require patterns and are easier to express with traditional PV languages; a large portion of your rule deck is legacy DRC script and you don’t want to change it; and so on. So it’s important that the PM and textual rules can coexist and are easy to integrate into a single PV flow, and it’s even better in a single DRC deck using a single PV tool.

Since most companies use design tools from multiple suppliers, it is important that the PV tool interfaces easily with all of the upstream and downstream tools in the flow. This becomes even more important as PM capabilities are being used on a broader range of checks (beyond spacing, fill, and litho hotspots) that may require interfacing to a greater range of external tools. For results that are consistent with your foundry, you may want to employ both the same rule and pattern decks they use, as well as the same PV tool used in process definition, since subtle implementation differences can create time-consuming exceptions to deal with.

You also want to use a tool that has high performance and scalability both in a standalone pattern matching flow or used as part of a combined DRC/pattern matching deck that can show results and support layout editing in a common work environment. And finally, you need a tool that provides graphical editing capabilities to help you build and manage your pattern library.

Conclusion

PV is based on a simple concept: certain geometric shapes in a layout can be difficult if not impossible to be manufactured with a given process. Therefore, we need a PV step to identify and remove these shapes from the design.

The problem is that the design rules required to identify problem patterns are becoming exponentially complex at advanced nodes. Pattern matching allows us to express the problem patterns directly in a natural 2D graphical language by drawing the shapes that must be avoided. PM-based verification not only makes it easier to express the design rules, but the whole physical verification definition process also gets simpler and moves faster.

Michael White is the product marketing director for Mentor Graphics’ Calibre Physical Verification products. Prior to Mentor Graphics, he held various product marketing, strategic marketing, and program management roles for Applied Materials, Etec Systems, and the Lockheed Skunk Works. He received an MS in engineering management from the University of Southern California and a BS in system engineering from Harvey Mudd College.

This file type includes high resolution graphics and schematics.

About the Author

Michael White

Michael White is Director of Product Marketing for Mentor Graphics’ Calibre Physical Verification products. Before joining Mentor Graphics, he held various product marketing, strategic marketing and program management roles for Applied Materials, Etec Systems and the Lockheed Skunk Works. Michael received a BS in System Engineering from Harvey Mudd College. He also holds a MBA/BS in engineering management from the University of Southern California.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: