Non-Volatile NRAM Nanotubes Deliver Endurance and Performance

Nantero’s nanotube-based NRAM technology has an impressive feature list. It has the read/write speed of DRAM with flash memory’s non-volatility but with significantly higher endurance. It can retain data for more than 1,000 years at normal temperatures. It is also amenable to the latest CMOS technology scaling below 5 nm as well as supporting MLC (multi-level cell) and 3D structures. Best of all it works with current CMOS fab technology.

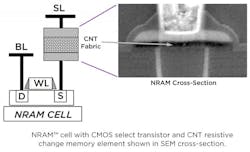

NRAM is based on film of crossed nanotube (CNT) deposited on a silicon substrate. Each cell can be switched between a low and high resistive state (Fig. 1) that is stable in excess of 300° C.

The CNT layer is etched using standard lithography techniques. A single cell has hundreds of nanotubes (Fig. 2). They are scattered, but proper alignment is required for it to act as a programmable storage device. Changing the cell’s state requires application of a programming voltage for a few picoseconds. Experimental chips have reached 1012 write cycles and 1015 read cycles.

NRAM addresses almost all aspects of storage, given its potential scalability and performance. It is especially well suited for embedded applications because it is compatible with conventional CMOS technology, allowing it to be employed in microcontrollers. Its wide operational temperature range will allow its use in rugged applications like automotive and aviation.

NRAM—like previous technologies such as FRAM, MRAM, and phase-change memory—has the potential to unseat the existing DRAM/flash combination that currently dominates computer technology. It remains to be seen whether it will be a winner or a niche player, but it is looking good so far. Nantero is currently licensing its technology. Initial chips are expected to be compatible with DDR4 interfaces.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: