LPDDR4 DRAM Meets Mobile Power and Performance Demands

Analysts estimate that the mobile device industry will ship 2 billion units per year by 2018, up from 1 billion in 2013. While consumers are driven to own the latest gadgets by the lure of bigger screens, better cameras, and new features, the key driver may be the growing use of mobile devices in more areas of people’s lives.

This file type includes high resolution graphics and schematics when applicable.

While the growth of the market is good news for mobile manufacturers, the relentless spread of applications is both an opportunity and a threat. In essence, the more tasks that people can complete on a mobile device, the more time they will spend on the device and the more frustrated they will become when the battery runs out. The problem is exacerbated because some of the latest apps, like those for fitness, are “always on” and commonly communicate with sensors, creating an even bigger power drain.

As the use of mobile devices increases, so do users’ expectations for higher performance and longer battery life. Current and near-future mobile devices support powerful CPUs, 4K video, lifelike and 3D graphics, and constant computation power. Still, users expect the battery to last longer.

Manufacturers could incorporate higher-capacity batteries, but that would mean bigger, heavier, hotter products, all of which are likely to turn consumers off. Until battery technology takes a quantum leap forward, chip design teams must use every available technology and design advantage to minimize power consumption while maintaining performance to keep consumers happy.

Organizational bodies for PCI Express, USB, HDMI, and DDR are all announcing higher data rates. PCI Express 4.0 offers 16 Gtransfers/s, USB 3.1 promises 10 Gbits/s, and HDMI 2.0 touts 18 Gbits/s, all of which will increase performance—but at what price to battery life? LPDDR4, the “low-power” DDR4 specification, is expected to define an interface up to 4.2 Gbits/s per pin parallel and up to 34 Gbytes/s per package, specifically addressing the high-performance, low-power needs of mobile devices.

More DRAM, More Power

After the display screen and application processor, DRAM memory is one of the biggest consumers of power within mobile devices. In addition, DRAM memory bandwidth increases in line with screen resolution and processor performance, which leads to even more power drain. Originally conceived for home entertainment and large TV screens, 4K video (3840 by 2160) has already found a place on the spec sheets of recent laptops. But the prospect of 4K for tablet devices is a true innovation.

LPDDR3 is the DRAM of choice for many of the latest smartphones, given that it supports bandwidth of up to 2133 Mbits/s and incorporates a number of power-saving features, including low standby and signaling power and 1.2-V operation. LPDDR3 won’t support the bandwidth and low-power needs of the forthcoming generation of devices, which is why the industry is hungry for the next generation: LPDDR4. Designed specifically for mobile applications, LPDDR4 SDRAM will be faster than the memory parts that go into today’s PCs and servers.

Coping with More Power Demands

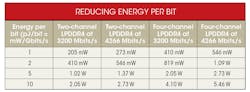

LPDDR4 promises more bandwidth: initially 3200 Mbits/s with the potential to increase to 4266 Mbits/s with future frequency extensions. The related JEDEC standard in development can support higher data rates by using a flexible two-channel per die, two-die per package architecture and low-voltage signalling technology. Low-power enhancements and a narrower address bus will reduce the energy required per bit (see the table). Transferring more bits, though, means that the overall power consumption may be higher than an LPDDR3 implementation at the highest speeds of operation. Because LPDDR4 will find a place in the highest-performance, most complex systems, power management becomes even more critical.

To avoid thermal issues, system designers can use strategies such as monitoring the SDRAM’s internal die temperature, increasing the refresh rate, and throttling back the SDRAM clock when it is detected that the die is about to overheat. This may only be necessary when the device is used during extremely compute-intensive tasks such as real-time gaming, which draws more power and increases the heat dissipated.

Accelerate Time-to-Market

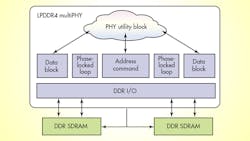

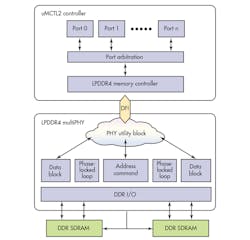

To help accelerate the delivery of mobile devices that meet mobile users’ demand for low power and high performance, the Synopsys DesignWare LPDDR4 intellectual property (IP) solution includes the LPDDR4 multiPHY with I/Os, the Enhanced Universal DDR Memory Controller, and verification IP (see the figure). Synopsys also offers hardening and signal integrity services to ease integration and accelerate time-to-market.

The LPDDR4 IP solution supports up to 3200 Mbits/s with low power consumption, which enables design teams to exploit the full bandwidth of the LPDDR4 standard to maximize system performance. It also supports switching between separately trained frequencies to tailor performance to meet the needs of the application while still minimizing power consumption.

The IP is backward compatible with LPDDR3 and DDR3/4 SDRAMs, which simplifies design transition from one SDRAM standard to the next. It supports all key LPDDR4 features, with multiple power-saving modes (including power-down, self-refresh, and deep power-down), as well as clock gating and selective power-down of parts of the physical layer (PHY) that are not in use.

The DesignWare LPDDR4 IP supports a split PHY implementation to permit designers to distribute the IP around the system-on-chip (SoC), optimizing the interface for area-efficient package-on-package (PoP) assembly and offering a low-risk evolutionary path from previous-generation mobile memories. Designers can take advantage of Synopsys’ DDR hardening and signal integrity services to harden the LPDDR4 multiPHY and to analyze the signal integrity of the entire system (PHY, SoC, package and system), easing IP integration and reducing potential risks.

Support for PoP reduces printed-circuit board (PCB) area in smartphones, while memory-on-PCB support allows for bandwidth and capacity expansion for tablets, notebooks, and ultraportable laptops.

Summary

LPDDR4 memory will be used in mobile devices to enable powerful computing, high-resolution video, larger displays with more pixels, and an enhanced user experience, all while maintaining battery life. To enable more rapid adoption of LPDDR4 for mobile platforms, designers can leverage Synopsys’ DesignWare LPDDR4 IP solution.

Marc Greenberg is the director of product marketing for DDR controller IP at Synopsys. He has 10 years of experience working with DDR design IP and has held technical and product marketing positions at Denali and Cadence. He has a further 10 years of experience at Motorola in IP creation, IP management, and SoC methodology roles in Europe and the United States. He holds a five-year master’s degree in electronics from the University of Edinburgh in Scotland. He can be reached at [email protected].

Graham Allan is the senior product marketing manager for DDR PHYs at Synopsys. He graduated from Carleton University’s Electrical Engineering program with a passion for electronics that landed him in the field of DRAM design at Mosaid in Ottawa, Canada. Beginning at the 64-kbit capacity, he worked on DRAM designs through the 256-Mbit generation. Starting in 1992, he was a key contributor to the JEDEC standards for SDRAM, DDR SDRAM, and DDR2 SDRAM. He holds over 20 patents in the field of DRAM and memory design. He can be reached at [email protected].

About the Author

Marc Greenberg

Director of Product Marketing

Marc Greenberg is the director of product marketing for DDR Controller IP at Synopsys. He has 10 years of experience working with DDR Design IP and has held technical and product marketing positions at Denali and Cadence. He has a further 10 years of experience at Motorola in IP creation, IP management, and SoC methodology roles in Europe and the United States. He holds a five-year master’s degree in electronics from the University of Edinburgh in Scotland.

Graham Allan

Senior Product Marketing Manager

Graham Allan is the senior product marketing manager for DDR PHYs at Synopsys. He graduated from Carleton University’s Electrical Engineering program with a passion for electronics that landed him in the field of DRAM design at Mosaid in Ottawa, Canada. Beginning at the 64-kbit capacity, he worked on DRAM designs through the 256-Mbit generation. Starting in 1992, he was a key contributor to the JEDEC standards for SDRAM, DDR SDRAM, and DDR2 SDRAM. He holds over 20 patents in the field of DRAM and memory design.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: