NXP and TSMC are making MRAM magic. The next S32 processors will be sporting magnetoresistive RAM (MRAM) instead of flash memory to handle on-chip, non-volatile storage. This new mix will use TSMC's 16-nm FinFET technology, and will debut in 2025. MRAM's performance can significantly improve things like write times compared to flash memory, which is important in automotive applications such as over-the-air (OTA) updates (Fig. 1).

MRAM has been trying to compete with flash memory that currently dominates the non-volatile memory (NVM) space. Flash will continue to be the go-to technology for external storage and on-chip storage for many applications, but it doesn't scale as well as MRAM with smaller transistor geometries. The 16-nm node looks like the crossover point.

MRAM also has significant performance benefits (Fig. 2). Like resistive RAM (RRAM), MRAM doesn't require an erase-before-write cycle like flash. That cuts down overhead, but MRAM's 6.25-MB/s write speed is significantly better than the competition. It is 10X that of flash memory. The 20X improvement over flash is due to the required erase cycle.

MRAM can perform up to a million writes before things start to degrade. It also has a 20-year retention at these rates. Flash storage needs to limit the number of cycles to reach this time period. RRAM supports fewer cycles but has a 15-year retention period, which is very good. Finally, MRAM and RRAM support single-bit-level changes. Systems using flash memory must read a sector, make a change, erase the sector, and write it again. That's a lot of steps and overhead, and it affects a whole sector.

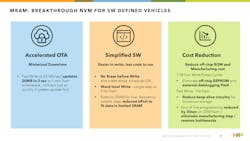

MRAM is important in automotive applications because updates in new vehicles can impact a significant number of processors within the car. A 20-MB update can be completed in three seconds versus a minute for flash memory. If multiple engine control units (ECUs) must be updated, then it's typical that all must complete their updates successfully or roll back to a known state. Reducing the update and roll back times reduces the time a car would be unavailable for operation.

Software support is also simplified because of the elimination of the erase cycle; it's simply a write cycle, single bit updates, and the ability to move storage from SRAM to MRAM (Fig. 3). The latter can be done for many aspects of an application where SRAM performance isn't required, such as data logging. It also helps in low-duty-cycle applications where a device wakes up, grabs some info, writes it to MRAM, and goes back to sleep.

The ability to handle this type of data-logging operation without going to off-chip memory can reduce the overall bill-of-materials (BOM) and the amount of power required. Using on-chip memory is also faster and more power-efficient. Luckily, MRAM scales nicely as transistor sizes are reduced.

For now, NXP is targeting its automotive applications, but this technology mix is applicable to any embedded platform especially as smaller transistor nodes are used to implement processors and system-on-chip (SoC) solutions.