This article is part of TechXchange: RISC V

By integrating hard-core RISC-V CPUs with its latest FPGAs, Microsemi, a Microchip company, has further bolstered its RISC-V support. This is the same approach that Intel/Altera and Xilinx have done with Arm cores and their system-on-chip (SoC) FPGA offerings. Microsemi also has an FPGA with a hard-core ARM Cortex-M3, but its Mi-V initiative has been pushing soft-core RISC-V support in its FPGA lines.

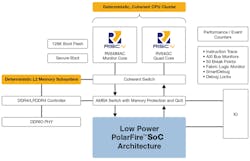

Microsemi’s 64-bit RISC-V SoC FPGA is based on its PolarFire FPGA. The approach has a number of advantages, including a simplified design that’s easier to secure. The design is immune to Spectre- and Meltdown-style attacks. The company has also included anti-tamper support, differential-power-analysis (DPA) resistant bitstream programming, cryptographic bound supply-chain assurance, physically unclonable function (PUF) support, a side-channel resistant crypto coprocessor, and a true random number generator. In addition, all memory has single-error-correction, double-error-detection (SECDED) support.

The RISC-V approach also provides a lower-cost migration path to an ASIC for those designs that are more geared to high volumes. The kicker is that these cores can be configured to provide deterministic operation.

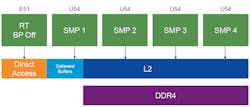

1. Microsemi’s PolarFire SoC sports five cores, including an E51 and four U54 RISC-V cores connected to a common L2 cache.

The PolarFire SoC consists of a flash-based PolarFire FPGA and five 64-bit RISC-V cores (Fig. 1). One is a SiFive E51 RV64IMAC core and the other four are SiFive U54 RV64GCs. SiFive has been delivering a number of different RISC-V cores to chip designers.

A coherent switch links the cores to the DDR4/LPDDR4 memory controller and the AMBA switch that’s connected to the PolarFire FPGA. There’s 128 kB of on-chip flash memory for applications in addition to secure boot support.

The E51 is designed as a control monitor with physical memory protection (PMP) unit while the U54 cores add a memory management unit (MMU) suitable for running operating systems like Linux. The cores have an in-order, five-stage pipeline. Each core can have features turned off, such as the branch predictor providing a deterministic execution environment. The 2-MB L2 cache can also be customized so that portions are locked down in scratchpad mode, enabling support for coherent message buffers (Fig. 2). These can be accessed by any core even if it’s not running in deterministic mode.

2. The RISC-V cores can be configured for deterministic operation and the L2 cache can be partitioned into direct access memory.

The ability to configure any core in this fashion provides developers with more flexibility. Various combinations may be used, such as the E51 running in deterministic mode while Linux runs on all four U54 cores. Alternatively, one of the U54 cores and the E51 cores could operate in deterministic mode with the other U54 cores running Linux. All can share all partitions of the coherent memory subsystem.

The I/O space also supports hardware partitioning. This allows the crypto hardware to be isolated with the E51 or maybe even one of the U54 cores.

The chips provide a robust debug environment. The FPGA has the SmartDebug dual-channel logic analyzer built in. The RISC-V cores have an instruction trace, 50 hardware breakpoints, debug locks, and a fabric logic monitor. There’s also an AXI bus monitor.

Microsemi is providing developers with complete access to the security features of the chip, including the secure-boot source code. This gives advanced developers the ability to check or replace this code to customize the secure-boot process.

The PolarFire SoC will not be available immediately, but developers can take advantage of the free Renode virtual development emulator model created by Antmicro. The emulator model supports debugging the entire processor subsystem.

Microsemi’s PolarFire RISC-V platform delivers secure, real-time, deterministic, asymmetric multiprocessing (AMP) support. It has impressive security and debug features in addition to RISC-V cores. Extended temperature versions will be available. The low-power, flash-based FPGA along with the low-power RISC-V cores provide a low-power solution that other platforms may find hard to beat.

Microsemi will be one to watch in 2019 when the chips are released.