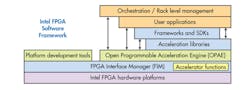

The Programmable Acceleration Card (PAC) series from Intel kicked off with its Arria 10-based board. Part of Intel’s solution that makes the hardware impressive is the open-source Open Programmable Acceleration Engine (OPAE), available on GitHub. OPAE runs on top of the FPGA Interface Manager (FIM). FIM manages the PAC hardware (Fig. 1).

1. The Open Programmable Acceleration Engine (OPAE) runs on top of the FPGA Interface Manager (FIM) to manage Programmable Acceleration Cards (PACs).

The system brings FPGA configurability to the enterprise and embedded systems. It allows integration with the operating system and, in turn, applications. The software handles configuration of the FPGA based on FPGA IP files that also contain metadata about the hardware requirements and acceleration functions made available to the software.

The Arria 10 PAC provided the hardware platform to make the software framework usable. The FPGA is linked to the processor complex using PCI Express.

The latest addition to the series is the PAC with Stratix 10 SX FPGA (Fig. 2). Stratix 10 SX incorporates a quad-core ARM CortexA53 complex in addition to the FPGA fabric.

2. The PAC with Stratix 10 board brings high-end configurable FPGAs to the party.

The boards include four DDR DIMMs for a total of 32 GB of off-chip memory. The 14-nm FPGA includes 2.8 million lookup tables (LUTs). The PAC has a pair of 100-Gb/s PCIe Gen 3 interfaces; the three-quarter slot board uses only 225 W.

The board can be used for artificial-intelligence chores, but is more likely to be employed for applications like Adaptive Micro-Ware’s video transcode, Megh Computing’s streaming analytics, and risk analysis. The software is now integrated with platforms like VMware vSphere 6.7 Update 1; drivers are being incorporated into the Linux. The integration with rack management and orchestration frameworks enables multiple boards to be incorporated into high-performance compute environments.

Intel is working to bring the Intel Workload Storefront to developers. It will provide a way to test and deploy FPGA-based services available from third parties. This would include per-node and metered licensing.

These platforms don’t make it any easier to develop a program for the FPGA, although Intel’s OpenCL FPGA support significantly simplifies certain applications already written for OpenCL. The hardware and software framework does make it much easier to deploy systems once the applications are developed.