Why LDPC Codes Aren’t Suitable for Industrial Storage

Low-density parity-check (LDPC) codes are a type of error-correction code increasingly used in applications requiring highly efficient information transfer over channels with the presence of corrupting noise like video broadcasting from satellites or earth-based transmitters. In the last 10 years, LDPC codes have also gained greater attention in the world of flash memory.

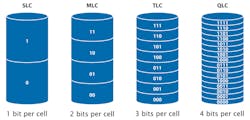

The Bose, Chaudhuri, and Hocquenghem (BCH) codes that were widely used for single-level-cell (SLC) and multi-level-cell (MLC) flash technologies weren’t able to deliver an acceptable performance given the limited spare area of today’s 3D triple-level-cell (TLC) and 3D quad-level-cell (QLC) flashes (Fig. 1). Thus, they were replaced with other codes with the capability to use soft-decoding like LDPC codes. As promising as these codes are for some applications, they do have two major drawbacks.

1. Different types of flash memory are available today. The more bits are stored per cell, the lower the data retention and the higher the amount of faulty bits. While SLC and MLC are mostly manufactured in planar flash technologies, TLC and QLC are manufactured in 3D technology.

LDPC Performance is Great in Some Areas, But Only Average in Others

LDPC code performance is excellent for input data with high error rates. Very few other codes achieve this level of performance as it even approaches the theoretical maximum, the Shannon Limit. On the other hand, their performance is rather mediocre for input data with very few errors.

In relation to the few input errors, failing error correction is quite frequent—other codes achieve significantly better results in this area. As a result, LDPC codes are used in situations where occasional errors are acceptable in the case of low input error rates, yet high performance for high error rates is needed (e.g., the terrestrial digital video broadcasting standard DVB-T). In this case, a failed correction will result in the wrong color of a few pixels in the video stream, which is acceptable. For the other case—a high amount of errors in the input data—the video stream will remain without interruption (e.g., a black screen) as long as possible.

This tradeoff explains the rising presence of LDPC codes in NAND-flash-memory controllers. The latest NAND flash technologies show very high error rates, especially those targeting the consumer market. LDPC codes are close to ideal for these requirements.

Still, there are other markets where occasional errors aren’t acceptable for input data with low error rates, such as the industrial market. A common criterion for system-level reliability is the JEDEC enterprise specification. It demands rates of less than 10-16 frame errors for the whole operating life.

As impressive as the performance of LDPC codes is toward the end of life of NAND flashes, it simply doesn’t achieve this requirement over the lifetime of the memory, i.e. over the varying bit error rates the flash memory delivers as input to the error correction—low in the beginning, high at the end of life.

LDPC Performance Can Only be Estimated

To cope with this demanding specification from JEDEC, the University of Applied Science Konstanz and Hyperstone developed a different error correction code based on a generalized concatenated code (GCC). It doesn’t outperform LDPC codes for high input error rates. However, it does show a significantly better performance for low and medium error rates.

The main advantage is that the performance can be calculated and therefore guaranteed for all input error rates, while the LDPC performance can only be estimated for low and medium error rates. A detailed explanation of this can be found in the free-to-download Fundamentals of Reliable Flash Storage white paper “Error Correction Codes.”

This means that in addition to its mediocre performance for low to medium input error rates, it’s not clear what exact level of performance the LDPC will deliver. This fact completely disqualifies it for the industrial and enterprise storage markets.

Error Correction for Highest Requirements

The error correction based on a GCC found in Hyperstone’s latest flash-memory controllers works hand in hand with a mechanism called calibration (Fig. 2). This mechanism ensures that the readout voltages of the flash-memory cells are always optimal, resulting in low to medium bit error rates over the complete lifetime of the flash memory.

2. Hyperstone’s latest SSD controller achieves a level of reliability that meets the needs of applications with very high requirements.

Consequently, the amount of data errors at the input of the error-correction unit remains within the optimal input conditions—the conditions in which the GCC error correction significantly outperforms an LDPC-based error correction. While calibration improves the system-level performance in combination with the GCC, it doesn’t boost LDPC-based error correction because it moves the input error rate from a favorable range to a less-favorable range for LDPC.

LDPC codes are the prevalent codes used in the error correction of flash-memory controllers. They’re excellent for consumer products, where an occasional error is acceptable. In industrial markets with high demands for reliability, they’re simply not suitable. On the other hand, the GCC in combination with an advanced calibration can meet the demanding requirements within the industrial arena.

Axel Mehnert is VP Marketing and Strategy at Hyperstone.