Generically, embedded test implies a test capability that has been integrated into a product. Of course, whether that product is an IC, a PCB, or a complete system, embedded test means different things. To partition the overall concept into manageable segments, it’s helpful to consider the test mechanism as well as how it is used.

Boundary scan 1149.1, also called JTAG, is a good example of a dual-purpose capability that supports specific test requirements and allows access to other functions. The interface specified by 1149.1 is built into ICs and PCBs and used to serially apply test vectors via the test access port (TAP). Successively connecting the test data in (TDI) pin on one IC to the test data out pin of another creates a long shift register through which test data can be applied and test results read out.

However, rather than have such a 1:1 correspondence between input and output, TDI data increasingly is being used to drive specific on-chip or on-board test circuitry. For example, many ICs such as serialize/deserialize chips include phase locked loops (PLLs) to translate from one clock rate to another. In this case, an embedded PLL built-in self-test (BIST) circuit can be configured through the TAP, perform its prescribed test functions, and then report the results via the TAP.

Figure 1. PLL BIST With Picosecond Precision

© 2010 IEEE

Figure 1 shows the interface between a six-output PLL and a PLL BIST circuit that operates in this way.1 Embedded test functions represent a further level of abstraction and often are accessed via JTAG.

The distinction between the use of JTAG and boundary scan is itself an example of this abstraction. Originally, the Joint Test Action Group (JTAG) was concerned with manufacturing faults encountered when soldering large ICs to PCBs. The straightforward goal they first addressed was to determine if all the IC pins were correctly soldered to the PCB. This is the function of the boundary scan cells that allow pin-to-PCB joints to be tested for continuity and shorts.

The TAP mechanism developed to apply test patterns and report results has proven remarkably adaptable to test requirements well beyond this initial concern. So, when the access mechanism is used for some purpose other than boundary scan, as it very often is, it’s more precise to call it JTAG. The distinction is avoided as well as lost by simply stating the appropriate 1149.x IEEE designation.

A very wide range of embedded test capabilities is grouped under the term embedded instruments and addressed by internal JTAG P1687 (IJTAG), a proposed extension to 1149.x. The objective is to standardize both the description of and access to these instruments in the same way that 1149.1 standardized boundary scan test. Companies with JTAG expertise, such as Intellitech and ASSET InterTech, have been instrumental in defining P1687 and provide test tools for its use.

The various types of BIST can be viewed as one class of instruments that P1687 covers. Ideally, BIST circuits are wholly self-contained and add no I/O pin overhead. An example is the power-on test performed by many systems. For logic BIST, a source of random test vectors is needed, and newer PLL BIST approaches may require a separate sampling clock input. BIST circuits always have an output, and it’s convenient to communicate this via JTAG.

Scan compression and decompression are additional forms of on-chip embedded test. The assumption underlying all test data reduction schemes is that the amount of critical test data in any test cube is small, the rest being random. Based on this understanding and the success of Dr. Bernd Koenemann’s innovations at IBM, several compression schemes have been developed and continue to be enhanced.2

Mentor Graphics’ Tessent™ TestKompress® is a good example of a scan technique that reduces the amount of data the ATE must provide. TestKompress embeds a special decompressor ahead of an array of scan chains. The decompressor generates pseudorandom data based on its feedback shift register structure while at the same time deterministically distributing the input ATE data to all the scan chains.

On the output side, the input ATPG data drives X masking circuitry ahead of the compactor. The end result is a high-coverage scan test with a large data-compression ratio. The number of pins required for I/O data can be as low as two, providing support for low pin-count testers or multisite testing.

Multiple Constraints Drive IC Test

A growing number of concerns affect the type and extent of test mechanisms and techniques developed for today’s ICs. Speed, power, and the design automation flow are near the top of the list.

Speed

High-speed circuits only work properly when the timing of all the constituent parts is correct. This usually implies that test circuitry cannot be allowed to disrupt the functional design. At a sufficiently high clock speed, even adding a test point is disruptive.

BIST approaches are good solutions for speed-related problems for a couple of reasons. They are by definition mostly if not wholly self-contained so don’t add lots of I/O routing or pin overhead. Equally important, they use the same technology as the circuit being tested so inherently have the same speed capabilities.

An example of a particularly demanding high-speed test technique is the PLL BIST approach presented at the 2010 International Test Conference. When a PLL is used to generate a clock, the amount of high-frequency jitter correlates well with the bit error rate (BER) likely to be associated with data links using that clock. The BIST circuit is required to measure PLL jitter with picosecond precision, corresponding to a very small BER.

Directly measuring the BER is impractical because it would take far too long to be economical. Instead, the clock is undersampled by a sampling clock set to a frequency very slightly lower than the PLL’s reference clock frequency. In general, “the resolution of the undersampling is equal to the difference between the period of the undersampling clock and the period of the nearest integer multiple of the PLL’s reference frequency, regardless of the PLL’s output frequency.”1

For example, a 99.99-MHz undersampling clock would be used with a 100-MHz PLL reference clock to give 1-ps jitter timing resolution. The reference clock period is 10 ns, and the undersampling clock period is 10.001 ns, giving a difference of 1 ps.

“The…BIST measures jitter, phase delay, duty cycle, output-to-input frequency ratio, lock time, and lock range and compares each measurement on-chip to upper and lower test limits serially shifted-in via a standard 1149.1 TAP interface. All of the BIST logic can be tested via scan path and by logic BIST.”1

Several comments throughout the IEEE paper relate to the wide range of constraints within which the PLL BIST design was developed. “Designing a BIST to measure near-picosecond jitter is an interesting challenge, especially if the BIST circuit must be simpler and have higher yield than the PLL and be synthesized and automatically laid out using only logic gates from a standard cell library…. The BIST’s silicon area was one-sixth of the PLL’s area…so its yield impact can be expected to be insignificant…. Jitter in the sampling clock path was minimized by minimizing the wire length and the number of clock buffers while minimizing total path delay and shielding the path from interfering signals wherever possible.”

Power

In response to the popularity of low-power, portable, battery-operated devices, several design techniques have been developed. One way to save power is to partition a design into parts that can be powered separately. Different levels of performance correspond to higher or lower voltage levels.

The many voltage domains that can be established in this type of design set boundaries that must be observed when inserting the test circuitry. A Synopsys whitepaper on the company’s DFTMAX™ and TetraMAX® tools states, “Multiple voltage domains require dedicated level shifter cells for all signal crossings between voltage domains, and scan chains are no exception. Thus, the scan chain architecture…should also reduce or eliminate individual scan chain crossings between voltage domains. Grouping and ordering scan chains without awareness of voltage domains could result in a huge increase in the number of level shifters required….”3

In addition, only a few of an IC’s functions may need to be available at a given time. It might be possible to turn off the others, a technique called power gating. When circuits are off rather than simply operating at a reduced voltage level, their previous states must be remembered so they can be reinstated upon application of power. This calls for additional retention cells. Also, any attached logic must be isolated to avoid loading. This requires isolation cells at each power-domain boundary.

“If the device will ever be tested with one or more power domains in an inactive state, it is critical that scan chains in any active power domain operate independently from those in an inactive state. Besides the scan chains, scan compression logic must consider power domains…. Synthesis must properly insert and connect complex sequential cells that incorporate both retention and scan functionality.”3

If the data applied to a latch isn’t changing, there’s no need for clocks following the one that first transfers the data level to the output. Clock gating saves power by minimizing the amount of capacitance that must be charged/discharged per clock cycle. Of course, it adds some complexity because clocks must be allowed to run when the data is changing, but many design tools provide automated clock gating insertion.

Power considerations also affect the actual test data. To ensure that the test-mode performance is representative of the mission mode, the power dissipated in both modes should be similar. One way this can be managed is to tailor the ATPG output. Instead of filling all the noncritical scan chain locations with random data, they could be filled by repeating the last critical data value. So, rather than a scan chain being filled with a critical 01 transition followed by 011001010 or a similar random sequence, the list of values would start 01 followed by 111111111.

This technique reduces the switching density and the degree to which the random data performs useful tests. Clearly, a degree of power tuning is possible, the trade-off being a larger number of test patterns and longer test time. Several EDA companies offer this type of ATPG capability.

Patrick Gallagher, architect and product engineering group manager at Cadence Design Systems, said that the Encounter Test Tool Set, specifically the Encounter DFT Architect, features the capability to control scan and capture switching to reduce average and instantaneous power without affecting test quality. The tools also support modular BIST of different power domains. In addition, the Encounter RTL Compiler provides fully automated power-aware scan stitching.

Flow

Although at first it may seem counterintuitive, the use of third-party IP doesn’t necessarily make test easier. As explained by Steve Pateras, marketing director, design to silicon marketing at Mentor Graphics, “…third-party IP cores…often consist of high-performance embedded processors such as those available from ARM. Highly optimized architectures and carefully tuned timing paths are required to achieve ever-increasing performance levels….” He continued, “Integrating design-for-test capabilities such as memory BIST and self-repair capabilities into these cores can affect performance levels because logic typically has to be inserted into functional paths.”

Mentor’s Tessent MemoryBIST product automatically inserts these capabilities into a design “without affecting design schedule, performance, or product quality,” according to Mr. Pateras. The design tool flow has been changed to include two additional inputs. The first file is provided by ARM and describes the specific access infrastructure between the standard interface ports and the memories within a core. It is called a core library file and includes information on addressing and pipelining.

The second file is a logical memory library file describing how memories have been implemented. This file provides the logical-to-physical mapping the BIST controller needs to generate patterns that achieve full defect coverage.

Tessent MemoryBIST is the type of tool used to deal with test insertion for third-party IP. Because IC design is so complex and relies upon an automated tool chain, the availability of compatible tools like this must be part of any IP selection process.

SynTest Technologies’ DFT-PRO Plus™ is an example of an integrated DFT solution and includes TurboDFT™, a tool for DFT insertion and stitching. In this context, stitching refers to the connection of DFT cores such as scan, memory BIST, logic BIST, IP, and JTAG. Very complex ICs are designed in a modular form, and to complete the process, all the various elements including the DFT cores must be interconnected.

Trends in PCB Testing

The various 1149.x enhancements and P1687 extensions are certain to shape PCB design and test for a long time. Nevertheless, these methods are not directly applicable to all PCB test requirements.

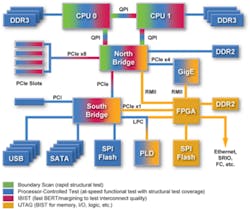

Figure 2. Improved Test Coverage by Combining Emulation and Boundary Scan

Courtesy of ASSET InterTech

A closely related technique that has become popular is JTAG emulation. Intellitech calls it JTAG-assisted functional test or JAF, ASSET InterTech simply refers to it as processor-controlled test (PCT), Corelis has developed a product called ScanExpress JET™ based on JTAG embedded test, and Goepel electronics named its implementation VarioTAP®. In each case, the idea is to test processor peripheral circuitry indirectly by using the processor’s JTAG port. Figure 2 shows how emulation boosts test coverage by providing access to circuitry that ordinarily could not be tested by 1149.x boundary scan.

As described in a Corelis whitepaper, “…The JTAG port offers the capability to access internal registers and memories as well as to apply breakpoints, similar to the emulators of the past, but without being intrusive, slowing the processor, or requiring target system hardware or software resources. JTAG provides all of the capabilities of a debugger while offering the potential for functional testing of a UUT at full operating speed. JTAG also opens up the possibility of marrying boundary-scan-based structural testing with functional testing.

“CPUs that include a JTAG debug port typically perform the following operations:

- Run

- Stop

- Step

- Write to registers and memory

- Read from registers and memory

- Exchange parameters with the JTAG host

- Display CPU status

The host software uses these features to download test/diagnostics routines into the CPU’s cache memory and the target memory. These routines execute at-speed and pass the test results to the host.”4

Ryan Jones, senior technical marketing engineer at Corelis, added, “JET has been expanded to include more CPU families…. Peripheral support also has been increased to include NAND Flash programming, serial bus testing, and interactive testing such as touchscreen calibration, audio playback, and button feedback.”

Although JET targets processors and their peripherals, more generic access and control are possible. According to Peter van den Eijnden, president of JTAG Technologies, the company’s “JTAG Functional Test (JFT)…a scripting language based on Python…can handle any register that can be accessed via the TAP…. JFT provides complete control over all types of embedded instruments and can be combined with a huge amount of available Python libraries providing the most flexible and powerful environment for deploying embedded instruments on a PCB.”

JTAG emulation deals with the processor and its peripherals. By using separate TAPs, additional PCB functionality can be simultaneously tested by controllers with multiple-TAP capabilities.

Choosing one JTAG emulation tool rather than another involves trade-offs. The Corelis JET, Goepel VarioTAP, and ASSET InterTech ScanWorks® PCT address particular processors. Of course you can customize the tools, but their main advantage is that they simplify JTAG emulation. Products with less specific capabilities may involve more work on your part.

The View From the Tester

It’s not only IC and PCB designers that have had to adapt to new requirements for embedded test. Peter Hansen, instrument product line manager at Teradyne, said, “Defense and aerospace designs of the last decade…, rich in embedded testability features, are making their way from initial production into the field. Unlike their predecessors, testing these [new] assemblies requires the transfer of large blocks of parallel and serial data. The parallel data represents information flowing from assembly to assembly related to sensor and display data. In contrast, serial data usually is associated with some use of the 1149.1 TAP.

“New Di-Series Digital Test Instruments have 256k-pattern memory behind every channel and provide an additional 8M-pattern sequentially addressed data memory per channel for data-intensive applications,” he continued. “When only a small number of signals are required, the sequential memory can be reconfigured behind one or two channels to provide a depth of up to 128 Mb of unique data.”

Summary

Embedded test in many forms supports ICs, PCBs, and complete systems. JTAG is one of the more popular access mechanisms and found at all three of these levels. IJTAG promises to standardize the treatment of embedded instruments as an extension of 1149.x, which will enable greater test development efficiency through instrument portability and reuse.

In addition, the various types of BIST continue to be improved to provide greater speed, better integration into existing tool chains, and higher performance. And, as Teradyne’s Mr. Hansen implied, the need for test data compression remains high as ICs continue to grow in size and complexity.

Because many ICs, PCBs, and systems have become very complex, designers rely on the comprehensive capabilities of their EDA tools and, in particular, test insertion. Test is developed at the RTL level along with the functional design. This can be accomplished by a separate tool like SynTest’s DFT-PRO Plus and then synthesized by tools such as those available from Mentor, Cadence, or Synopsys. These companies also have their own DFT tools.

Embedded test is equally as important as functional design. Even large, expensive ICs have to be tested quickly, and the many varieties of embedded test make this possible. In addition, well-designed embedded test supports IC, PCB, and system health checks and diagnosis throughout a product’s lifetime, not just during manufacturing or initial deployment.

References

1. Kinger, R., Narasimhawsamy, S., and Sunter, S., Experiences with Parametric BIST for Production Testing PLLs With Picosecond Precision,” IEEE Proceedings International Test Conference, 2010.

3. Hay, C., “Testing Low Power Designs With Power-Aware Test,” Synopsys, 2010.

4. “Using JTAG Emulation for Board-Level Functional Test,” ScanExpress JET Whitepaper, Corelis.

| FOR MORE INFORMATION | CLICK HERE | |

| ASSET InterTech | ScanWorks PCT | CLICK HERE |

| Cadence Design Systems | Encounter DFT | CLICK HERE |

| Corelis | ScanExpress JET | CLICK HERE |

| Goepel electronics | VarioTAP | CLICK HERE |

| Intellitech | IJTAG tools | CLICK HERE |

| JTAG Technologies | JTAG Functional Test> | CLICK HERE |

| Mentor Graphics | Tessent TestKompress | CLICK HERE |

| Synopsys | DFTMAX | CLICK HERE |

| SynTest Technologies | DFT-PRO Plus | CLICK HERE |

| Teradyne | Di-Series Test Instruments | CLICK HERE |