Who is using RISC-V? Judging from this year’s RISC-V Workshop, it appears many more firms have decided to enter the fray—with more to come.

Nvidia gave a presentation about how its proprietary Falcon (Fast Logic CONtroller) core will be replaced by RISC-V cores. Falcon is a RISC CPU used in a number of Nvidia’s chips, such as the Jetson TX2. Unfortunately, Falcon has limitations, including a 32-bit address space and no thread protection. RISC-V addresses the limitations with a 64-bit address space as well as features like ECC/parity support, an extensible ISA, and better security. The implementation will use the RV64IM_Sdef ISA.

SiFive has been a leader in the RISC-V space. Its HiFive1 board holds an FE310 RISC-V processor, one of the only commercially available RISC-V chips available. Among the company’s presentations at the workshop was one about an External Debug Definition for RISC-V. The definition allows for the incorporation of more powerful debugging support without requiring proprietary support and toolchains. Arm has a similar modular approach for its debug and trace facilities. The basic set of features in version v0.13 include selecting Harts, Halt – Resume, abstract commands, access to the program buffer, single-step support, debugging across reset/power down, and triggers.

SiFive’s competition has become fiercer, too, with more companies delivering RISC-V-based designs. For example, Syntacore presented its SCRx family of RISC-V cores. It starts with the SCR1, a minimal system that uses fewer than 15k gates. The top-end SCR5 supports virtual memory, SMP, and Linux, and runs at 1 GHz using 28-nm technology.

1. Here’s an example of using an embedded FPGA with Achronix SpeedCore technology in a RISC-V-based SoC.

Andes Technology unveiled its AndesCore family. The 32-bit family includes platforms like the N705. The N705 has a feature called PowerBrake, which allows the CPU clock rate to be dynamically throttled. These are features found in most high-performance processors, but aren’t part of the RISC-V definition because RISC-V is simply an ISA definition. These features are implementation-specific and transparent to the ISA. The AndeStar family uses RISC-V as a base subset.

The AndesCore NX25 moves into the 64-bit space. It has a five-stage pipeline, dynamic branch prediction, and local memory and cache with parity/ECC protection. It also features PowerBrake support, as well as support for StackSafe stack integrity and CoDense compact code.

AndesCores are showing up in a number of projects. Wave Computing’s Dataflow Processing Unit (DPU) uses an AndexCore as a control processor. The DPU, which targets machine-learning applications, consists of thousands of processing elements (PE).

FPGAs continue to play a major part with RISC-V adoption. I’ve already written about Microsemi’s Mi-V environment designed to bring FPGA-based RISC-V to software developers. Achronix is also supporting RISC-V with its Speedster FPGA family, as well as the custom SpeedCore platform. Of course, a RISC-V SoC could also include an embedded FPGA using SpeedCore technology (Fig. 1). The example shows a SiFive U500-based architecture.

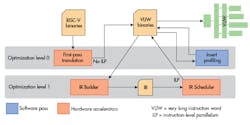

2. Dynamic binary translation of RISC-V code to run on a VLIW platform requires hardware support.

One interesting presentation was given by Rokicki Simon, Steven Derrien, and Erven Rohou from the Université de Rennes 1 and Inria Rennes entitled “RISC-V Hardware-Accelerated Dynamic Binary Translation.” It essentially takes RISC-V code and runs it on a VLIW platform using hardware support (Fig. 2).

RISC-V is still the new kid on the block, and lots of competition comes by way of Arm. It offers many advantages, and more in the industry have taken note and making use of them.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: