Xilinx’s Versal family has been expanded with the addition of the Premium Series (Fig. 1). This adaptive compute acceleration platform (ACAP) pushes the current Versal family boundaries across the board from SERDES performance to fabric and interconnect support. The new chips will be built by TSMC using the company’s 7-nm process.

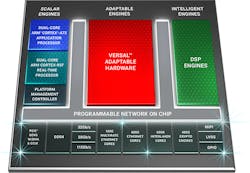

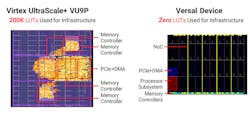

Its network-on-chip (NOC) links the FPGA fabric with an array of high-speed interfaces, DSP engines, and a processor complex built around dual Cortex-A72 and dual Cortex-R5F cores. The NOC provides a faster and more efficient interconnect because it eliminates the need for additional lookup tables (LUTs) to facilitate the interconnect (Fig. 2). A platform manager controller coordinates the operation of the entire system.

The communication support makes the Versal Premium stand out. With the inclusion of 32.75G NRZ GTYP transceivers, the system targets 5G wireless and high-speed wired networks such as 600G Ethernet, PCIe Gen5, and 600G Interlaken. New 112-Gb/s, PAM-4 GTM transceivers can handle 800G networks. The system also supports 58-Gb/s PAM-4 for 400G Ethernet support and 32-Gb/s NRZ for 100G support.

The chips have multiple 400G high-speed crypto (HSC) engines. The HSC engines integrate AES-GCM encryption/decryption, MACsec, and IPsec to provide multi-layered security at line rates.

The processor complex has 256 kB of ECC memory on-chip. It has access to Ethernet ports, UARTs, CAN-FD, USB 2.0, SPI and I2C interfaces. The top-end VP1802 Versal Premium includes over 14,000 DSP blocks. These enhanced DSP engines provide support for a variety of data types, including single- and half-precision floating-point and complex 18x18 operations. The blocks are backward-compatible with Xilinx UltraScale+ devices.

The PCI Express interfaces also support CCIX and CXL, which are hardware accelerator interface standards built on PCI Express Gen 5 platforms. They provide cache-coherent interfaces that allow platforms like Versal Premium to coexist with processors and GPGPUs on an even playing field. Subblocks provide efficient CCIX/CXL support.

Versal Premium is still a bit away from general availability. Tools will be available later this year, including development platforms, but silicon will ship in the middle of 2021. The integration with high bandwidth memory (HBM) will build on a Premium base with fast, on-chip memory (Fig. 3). Still, the current Premium platform delivers 123 TB/s of on-chip memory bandwidth with its 1 Gbit of tightly coupled memory (TCM). A DDR4 controller manages off-chip memory.

Versal Premium is supported by Xilinx’s Vivado Design Suite and the Vitis software-development platform. The Versal family supports dynamic function exchange (DFX), which enables kernel configurations to be changed in milliseconds. The reconfiguration of the FPGA and DSP blocks can be accomplished on a subset of the system, allowing the remaining sections to function normally.