RISC-V is a RISC instruction set standard that has been used to develop open-source processors (see “RISC-V (Five) Is Alive!”) in addition to proprietary implementations. It’s also the primary soft-core processor architecture for Microsemi’s FPGAs. Microsemi offers hard-core FPGAs, too, and supports other soft-core architectures like ARM’s Cortex-M1.

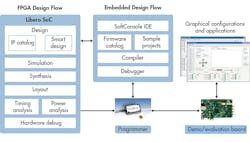

Developing and working with Microsemi’s a soft-core processor usually encompasses the Libero SoC FPGA design tool and the Eclipse-based SoftConsole integrated development environment (IDE), in addition to the FPGA platform (Fig. 1).

1. RISC-V development flow with Microsemi FPGAs starts with Libero for hardware design and the SoftConsole IDE for software design.

SoftConsole 5.1 is the latest incarnation and it has support for the range of RISC-V platforms. Developers can select the RISC-V configuration using the SoftConsole plug-in (Fig. 2). For example, the architecture supports 32-, 64- and 128-bit register set in addition to single, double and quad floating point support. SoftConsole targets 32- and 64-bit platforms that are available at this time. The Compressed Instruction set is adds a 16-bit instruction format to the mix that has more limited direct register access but it can reduce code size.

Libero and SoftConsole are linked via configuration files so that the Libero FPGA design, which includes a collection of peripherals and cores, can provide the details to the IDE. In turn, the compiler will be able to support the hardware.

Microsemi delivers its software in easy-to-install packages to minimize any integration chores. SoftConsole 5.1 supports Windows and Linux hosts including Windows 7 and 10, CentOS, Red Hat Linux, Ubuntu, and OpenSUSE. These include standalone installers simplifying installation. SoftConsole 5.1 is based on Eclipse Luna 4.4 SR2 and CDT 8.6.0 for C and C++ support. Support for target operating systems will eventually include FreeRTOS, SafeRTOS, LiteOS, and Micrium µC/OS II and III.

2. SoftConsole’s RISC-V Eclipse plug-in lets developers select the target configuration capabilities so that the compiler generates the appropriate code.

SoftConsole also comes with a firmware catalog of drivers for soft peripherals like PWMs and serial ports that can be used in the FPGA. These drivers are MISRA and Blackberry QNX Neutrino RTOS-compliant. MISRA C is a coding standard initially targeting safety in automotive environments, but also has been used for embedded applications (see “MISRA C:2012: Plenty Of Good Reasons To Change”).

The debugger supports Microsemi’s SmartDebug as well as OpenOCD. OpenOCD allows the toolset to be used with other RISC-V platforms in addition to Microsemi FPGA targets. SoftConsole will work with Microsemi’s PolarFire, RTG4, and IGLOO2 FPGAs. It also supports SiFive’s HiFive1 based on the first RISC-V microcontroller (see “First Open-Source RISC-V Chip Arrives”).

RISC-V has a number of advantages over the competition. For example, its open-source nature means the RTL is available for viewing compared to ARM Cortex-M1, which uses encrypted RTL. The Microsemi RISC-V implementations have no licensing fees regardless of how many cores are utilized in a design. Likewise, designs that migrate to an ASIC are also royalty-free.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.