Flash continues to dominate non-volatile memory (NVM), but it shares the storage space with volatile memory—including SRAM and DRAM that beat it in performance. However, other technologies are making their presence felt. In particular, MRAM provides the endurance and speed of SRAM and DRAM while keeping the NVM advantage of flash. So far, though, the challenge with MRAM has been cost and capacity compared to existing SRAM and DRAM.

Leading the way technology-wise for NVM MRAM is spin-transfer torque (STT). This form of MRAM has been successful in niche markets where its current capacity and cost are advantageous, such as in SAS controller cache memory. The use of MRAM eliminates the need for supercaps to allow DRAM cache to be saved to flash memory when there’s a power outage.

Spin Transfer Technologies' Precessional Spin Current (PSC) looks to take MRAM to the next level. It has a higher data delta and lower write currents compared to STT. For SRAM, MRAM may actually be smaller by up to 80% in sub-10-nm. There’s no bit-cell leakage, but it still doesn’t match SRAM’s speed. Of course, PSC MRAM is non-volatile. For DRAM, MRAM can lower the power requirements since no refresh is required.

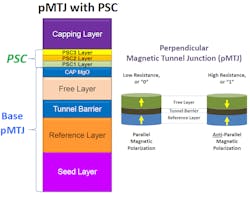

1. The Precessional Spin Current (PSC) design augments the usual the perpendicular magnetic tunnel junction (pMTJ) design by adding PSC layers.

PSC adjusts the perpendicular magnetic tunnel junction (pMTJ) design by adding some PSC layers (Fig. 1). The additional layers significantly improve data retention and stability while also enhancing read/write operations. The layers are electronically and magnetically coupled to the free layer. The process is compatible with conventional pMTJ stacks currently in use and add only 3 to 4 nm to the cell height.

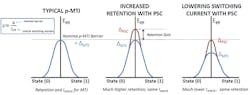

The additional retention gain provided by PSC can be used to increase data retention using the same current, or a lower current can be used while maintaining existing retention characteristics (Fig. 2). The PSC technology can boost STT for any pMTJ by 40% to 70%. And it will improve data retention by a factor of 10,000. In fact, the benefits of the approach actually become more enhanced as the process node decreases.

2. The PSC’s additional retention gain can be utilized to boost retention or lower the switching current.

PSC also reduces the read disturb error rate by up to five orders of magnitude. On top of that, it increases the thermal energy barriers by 50% with a corresponding increase in data-retention time of greater than four orders of magnitude while reducing the switching current.

“There is a huge demand for a memory with the endurance of SRAM, but with higher density, lower operating power, and with non-volatility. We believe the improvements the PSC structure brings to STT-MRAM technology will make it a highly attractive alternative to SRAM for these reasons,” says Mustafa Pinarbasi, CTO and SVP of Magnetics Technology at Spin Transfer Technologies. “We are excited to enable the next generation of STT-MRAM and to shake up the status quo of the memory industry through our innovation.”

STT-MRAM is currently available from a number of foundries, including TSMC, Samsung, and GlobalFoundries. PSC has yet to be incorporated into production designs, but its advantages make it a likely addition in the near future, so stay tuned.