The latest motherboards sport PCI Express (PCIe) 4 (Fig. 1). PCI-SIG’s PCIe 5 is now on the books and will likely replace PCIe 4 in PC and server motherboards as well as other devices with top-end processors. A 16-lane (x16) PCIe 4 delivers 64 GB/s of bandwidth.

1. PCI Express 4 is now ubiquitous in motherboards.

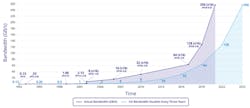

CPU clock speeds may have started to level off, but PCI Express bandwidth is on track to double every three years (Fig. 2). PCIe 5 x16 will deliver 128 GB/s of bandwidth and the forthcoming PCIe 6 will double this to 256 GB/s. All of these performance jumps are accomplished while providing backward compatibility.

2. PCI Express has delivered backward compatibility while doubling bandwidth every three years.

PCIe 6 is barely on the drawing board and won’t be standardized or mainstream for years, but it’s on the PCI-SIG’s roadmap. Keeping up PCIe’s backward compatibility will be a challenge in this next step, as the encoding scheme will shift from NRZ to PAM 4. This is on par with other high-speed systems like Ethernet. The other challenge will be keeping the distance capabilities of PCIe 4 and PCIe 5.

PCIe 6 will require more robust forward-error-correction (FEC) support to maintain low latency, a hallmark of PCIe. The standard is targeted for 2021.

PCIe is the basis for a number of other standards, such as NVM Express (NVMe) used for storage devices versus peripherals that are the target of PCIe. PCIe is also the basis for two peer-to-peer communication standards, including the Compute Express Link (CXL) and the Cache Coherent Interconnect for Accelerators (CCIX). These are maintained by the CCIX Consortium and CXL Consortium. They both bring cache-coherent memory support to PCIe.

NVMe now dominates high-performance storage, such as solid-state drives that are typically based on flash-memory technology. M.2 and U.2 form factors take advantage of NVMe in addition to PCIe sockets found on motherboards.

CXL and CCIX are designed so that devices like machine-learning (ML) accelerators can take advantage of a standard interface. Most peer-to-peer processor interconnects are proprietary and designed specifically for processors. FPGAs are the first devices to leverage CXL and CCIX.