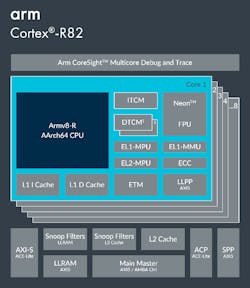

Arm’s Cortex-R series, which targets real-time applications, has been a 32-bit platform since its inception. However, the addition of the Cortex-R82 pushes it into the 64-bit space (see figure). The Cortex-R52 brought multicore support with a 32-bit flair, but it only provided a memory protection unit (MPU) like prior versions of the R series. This is less of an issue for the application space where deterministic, real-time support is key. Likewise, the R series is typically part of a system-on-chip (SoC) that often include complementary Cortex-A and Cortex-M processor cores.

There’s a plethora of targets for the Cortex-R82. The Cortex-R is heavily used in the automotive space, where ASIL certifications are also the norm. Almost any real-time application that requires high-end computation support will be a Cortex-R82 candidate.

The Cortex-R82 adds a host of new features, including a virtual memory management unit (MMU) that allows operating systems like Linux to run on the platform. Real-time incarnations of Linux exist, but that’s not necessarily the use case for the Cortex-R82. Instead, it can easily handle a mix of operating systems and applications—the platform has the ability to partition and manage a combination of real-time and application-oriented software.

Virtual-memory support makes a Cortex-R82-only SoC platform practical for many applications. Nonetheless, chip designers will likely continue to combine Cortex-R, Cortex-M, and Cortex-A. What this does accomplish, though, is make it easier to integrate a system with Cortex-A and Cortex-R cores, since they have the same memory capabilities. Past SoCs with 64-bit Cortex-A and 32-bit Cortex-R required interesting memory interactions. Cortex-M cores are still only 32 bits, but their applications are often more of a black box when viewed from a Cortex-A application.

The Cortex-R82 can address up to a terabyte of memory. The MMU is optional as are many parts of any Cortex platform. One feature that Cortex-R developers can take advantage of is tightly coupled memory (TCM) for data and instructions. TCM is more efficient and deterministic compared to a cache.

Instruction and data access utilize a shared AXI5, 256-bit, low-latency RAM (LLRAM) port. Peripheral access uses a shared AXI5 64-bit Shared Peripheral Port (SPP) plus a per-core AXI5 32-bit low-latency peripheral port (LLPP).

The Corex-R52 was the first to add lock-step support to the Cortex-R family. This allows a pair of cores to run the same application with outputs being checked. The configuration is often utilized in high-reliability and safety applications.

The Cortex-R82 can handle symmetric multiprocessing (SMP) that’s normally used with operating systems like Linux as well as asymmetrical multiprocessing (AMP) where cores are dedicated to specific applications.

The processor cores are based on the Armv8-R architecture that’s compliant with the Arm8.v-A extensions. The cores employ an eight-stage, in-order, superscalar instruction pipeline with direct and indirect branch predication support. The architecture is compatible with Arm TrustZone. ECC memory support is optional.

Debugging logic supports Armv8-R AArch64 with debug over power-down. A cross trigger interface (CTI) handles multiprocessor debugging. Arm’s CoreSight Embedded Logic Analyzer is optional as well. The system supports ELA-600 for advanced debug capability and signal observability.

Performance Monitors Extension capabilities allow for software profiling and performance debugging based on the PMUv3 architecture. The Trace Embedded Trace Macrocell (ETM) is compliant with the ETMv4.5 standard. The system also supports memory built-in self-test (MBIST) for testing memories at boot time.