Automotive SoC Brings Functional Safety to CNN Accelerator Cores, ASIL D Control

What you'll learn:

- What are the key components of the V3U SoC?

- What is the Freedom from Interference mechanism?

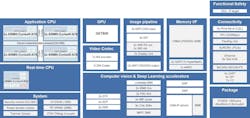

In one of the sessions at the recently concluded International Solid-State Circuits Conference 2021 (ISSCC 2021), Renesas presented a system-on-chip (SoC) that can do all of the main processing tasks for autonomous driving (AD). The device achieves 60.4 trillion operations per second (TOPS) and 13.8 TOPS/W from a 12-nm process. These technologies have been applied in the company’s latest automotive SoC, designated R-Car V3U.

Based on the Renesas R-Car Gen 4 architecture, the V3U offers scalability from entry-level applications up to highly automated driving systems. Available for advanced driver-assistance systems (ADAS), the part allows for electronic control units (ECUs) that are air-cooled, which brings advantages in weight and cost.

In addition, since signal processing from object identification to the issuing of control instructions constitutes the bulk of the processing load in AD systems, achieving the functional safety equivalent to ASIL D—the strictest safety level defined in the ISO 26262 automotive safety standard—is a notable feature.

With the large computational complexity of convolutional neural networks (CNNs), designers are looking for platforms that are as fast and energy-efficient as possible. Renesas says the SoC builds on its previous IP, enhancing CNN processing performance by four times compared to the previous generation.

The R-Car V3U has 2 MB of dedicated memory per CNN accelerator core, for a total of 6 MB of memory. This reduces data transfers between external DRAM and the CNN accelerator by more than 90%.

Integrated safety mechanisms provide fast detection and response for random hardware faults. This makes it possible to achieve ASIL D metrics as well as reduce design complexity, time to market, and system cost. A mechanism that enables software tasks with different safety levels to operate in parallel on the SoC without interfering with each other bolsters functional safety for ASIL D control.

Freedom from Interference

Renesas has developed a Freedom from Interference (FFI) support mechanism that monitors all data flowing through interconnects in the SoC and blocks unauthorized access between tasks. Achieving FFI between software tasks is an important aspect of meeting functional-safety standards. When software components with different safety levels are present in the system, it’s essential to prevent lower-level tasks from causing dependent failures in higher-level tasks.

In addition, an issue of particular importance in SoCs is ensuring FFI when accessing control registers in various hardware modules and shared memory. This enables FFI between all tasks operating on the SoC, making it possible to realize an SoC for ASIL D applications capable of managing object identification, sensor fusion with radar or LiDAR, route planning, and issuing of control instructions.

The ISO 26262 automotive functional-safety standard specifies metrics for ASIL D at 99% or above for the single point fault metric (SPFM) and 90% or above for the latent fault metric (LFM). That means an extremely high detection rate is required for random hardware failures.

Both reduced power consumption and a high failure detection rate are achieved by combining safety mechanisms suited to specific target functions. Incorporating these mechanisms into the R-Car V3U is expected to enable the majority of the SoC’s signal processing to achieve ASIL D metrics. An SoC that satisfies ASIL D metrics is capable of independent self-diagnosis, reducing the complexity of fault-tolerant design in an AD system.

The R-Car V3U also supports a wide range of programmable engines. These include DSP for radar processing, a multi-threading computer vision engine for traditional computer-vision algorithms, image signal processing to enhance image quality, and additional hardware accelerators for key algorithms such as dense optical flow, stereo disparity, and object classification.

The R-Car V3U delivers flexible deep-neural-network (DNN) and AI machine-learning functions. Renesas says its architecture is able to handle any state-of-the-art neural networks for automotive obstacle detection and classification tasks while maintaining 60 TOPS with low power consumption and an air-cooling system. According to Renesas, the SoC also is optimized for intelligent driver systems such as driver monitoring, park assist, and occupant sensing.

Dev Environment and Tools

Renesas has developed an open and integrated development environment to take advantage of the R-Car platform’s built-in hardware as well as its low power consumption and deterministic real-time software. All of which enables fast time to market for computer vision and deep-learning-based solutions.

Debugging and tuning tools for heterogeneous multicore hardware are available to assist software development while a large set of example applications and online education resources help engineers with their design process. Qualified compilers and code generators for compliance with functional safety and cybersecurity requirements assist development of safe and secure software.

Engineers also can combine the R-Car V3U with Renesas’s RH850 microcontroller, integrated power-management ICs, and power transistor devices to access key components required for ADAS and AD ECUs.

Samples of the R-Car V3U SoC are available now. Mass production is planned for the second quarter of 2023.