Infineon Rolls Out First NOR Flash Memory with LPDDR Inside

This article is part of the TechXchange: Smart and Secure Storage.

Modern cars are among the most complex electronic systems in the world. As software comes to dominate more of the system, the millions of lines of code inside them need to be safely executed in real-time by the hardware under the hood.

Infineon, one of the leading manufacturers of automotive-grade NOR flash-memory chips, said modern cars are facing a memory problem—one that stems from the demand not only for more memory capacity in cars, but also faster performance.

The company is rising to the challenge with what it called the world’s first NOR flash memory that uses DRAM’s LPDDR (low-power double-data-rate) interface. The Semper X1 brings up to 20X more performance than NOR flash based on the SPI bus widely used today.

Due out by 2024, the Semper X1 enables high-end processors at the heart of modern cars to execute code from external flash memory as fast as—and potentially faster than—from flash embedded in the processor.

Under-the-Hood Hardware

As the world enters the age of “software-defined vehicles,” new hardware architectures are taking shape.

Today, more than 100 electronic control units (ECUs) are distributed throughout a modern car. Each one only has enough computing resources on hand to do a single job at a time. As a result, everything inside the vehicle is becoming vastly more complex.

In turn, many automakers are moving to “domain-based” architectures that unite these single-use modules—and the microcontrollers (MCUs) inside them—into a smaller group of “domain controllers.” These controllers use high-performance chips to control several related jobs at once, giving them more than enough power to take care of assisted-driving and related safety-critical features plus other types of workloads.

One of the alternatives is a “zonal” architecture, where a central high-end computer unit acts as the car’s control center. It’s attached to the sensors and other systems over networking gateways that connect securely over Ethernet. Data is funneled from different parts of the vehicle to be processed by a series of “zone controllers,” which in turn communicate with the central control unit to execute commands.

In March, Infineon said it plans to work with Tier-1 Continental to create “zone controllers” for use in future cars. These boxes will act as the interface between high-performance computers, sensors, and actuators.

“With our new architecture solution, we are making the vehicle fit in the future," said Gilles Mabire, CTO of Continental’s automotive unit. “The growing variety of vehicle functions requires more and more computing power and increasingly complex software applications.”

These “domain” and “zone” controllers are designed to safely run several separate functions—for instance, those related to the powertrain, infotainment, or chassis—at once. Instead of running inside separate real-time MCUs (with embedded flash), they run in separate software containers on different cores in a single high-performance microprocessor (without embedded flash), thus reducing the number of physical boxes in the car.

These units not only have to handle vast amounts of data, but they also must process it in real-time to run safety-related workloads, ranging from braking and steering to controlling the battery-management system (BMS) or traction inverter in future EVs.

External Flash Execution

Today, the MCUs used in cars tend to execute from embedded flash. But placing the flash and other types of automotive-grade non-volatile memory (NVM) inside a processor is no longer viable at advanced process nodes used by the likes of Qualcomm’s “Flex” SoCs, Infineon’s Aurix SoCs, NXP’s S32G, and other similar chips. The cost of embedded flash is prohibitively high at these nodes, and it’s a struggle to scale bandwidth.

On top of that, more flash memory is necessary to handle all of the software (comprised of tens of millions of lines of code) taking over modern cars. One possibility is to use external NOR flash as expansion memory.

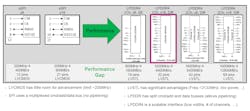

The problem? The industry-standard SPI interface used to attach external NOR flash lacks the performance of embedded flash. Consequently, it’s not ideal when it comes to executing code.

As it stands, it’s challenging to improve the clock frequency of SPI to more than 200 MHz, which is out of step with the high-end processors designed for future cars that are usually clocked at more than 1 GHz.

To execute code from external memory as fast as embedded flash, you can use SD-DRAM or another type of memory. Or you can upgrade the connectivity interface in the NOR memory itself, keeping all of flash’s other advantages.

Infineon said Semper X1 solves the challenge by using the same LPDDR interface as DRAM, enabling customers to move what was once computed inside a processor to external flash memory in real-time.

Semper X1 brings a wide range of improvements over existing NOR, according to the company, including 20X faster performance for random access than alternatives. The NOR delivers 3.2 GB/s of bandwidth over an Octal SPI NOR that runs at 400 MB/s—and it can do so without consuming excessive power, which is vital in EVs that have limited battery life to spare. In addition, Infineon said it’s 5X faster from command request to read data.

New Industry Standard?

Jim Handy, semiconductor analyst at market research firm Objective Analysis, said the LPDDR flash memory from Infineon is a completely new class of NVM for the automotive market.

He explained that the LPDDR interface that the Semper X1 takes from DRAM enables real-time execute-in-place (XIP). Code is executed directly from the flash instead of copying it into RAM before processing it.

According to Infineon, the ability to execute from external flash in real-time also opens the door to upgrade Semper X1 independently of the microprocessors in the car and use the best process node for each chip.

High-end chips at the heart of future cars will allow companies to continuously upgrade the vehicles over time and add features or services (or remove existing ones) using over-the-air (OTA) updates, a la Tesla.

Infineon said the Semper X1 is based on its “multi-bank” architecture—any of the cores in the high-end processors at the heart of the vehicle can access any of the banks in the memory at any time. As a result, the NOR flash can run remote updates of the firmware without having to shut everything down.

Importantly, the company also is keeping functional safety in mind with the Semper X1. The NOR flash is rated ASIL-B, and it supports advanced error correction code (ECC) and other safety features.

The Semper X1 is now sampling. Mass-production quantities are due to be available in 2024.

Long-term, Infineon is working with memory-chip suppliers, memory-controller IP vendors, and other industry players to expand the ecosystem around Semper X1 and future flash chips with LPDDR.