160 Time-Predictable Cores Escalate Car Computing Capability

Today’s automobiles and future self-driving cars will need a tremendous amount of computing power while meeting strict safety standards. Multicore and many-core solutions will support the software necessary to provide safe and secure transportation systems. In particular, a number of these applications require predictable, real-time performance.

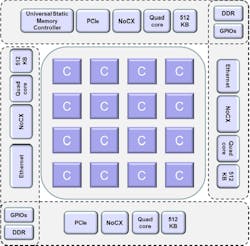

Kalray’s “Coolidge” Massively Parallel Processor Array (MPPA) chip contains up to 160 time-predictable, 64-bit cores for ASIL-B automotive applications. It also meets the ISO 26262 standard. Its network-on-chip (NoC) architecture employs a 2D-wrapped-around torus communication structure to link the compute clusters and peripherals (Fig. 1). A single chip will deliver nine teraFLOPS (TFLOPS) of performance while still allowing the system to handle real-time applications.

1. Kalray’s MPPA network-on-chip uses a 2D-wrapped-around torus communication structure to link the compute clusters and peripherals.

The architecture is similar to other many-core solutions. It groups cores in compute clusters connected by the NoC to adjacent clusters and the peripheral banks on the periphery of the chip. Peripherals include interfaces such as PCI Express and automotive communication interfaces. Some of the banks also feature timers and general-purpose interfaces like UARTs, I2C, and SPI.

The NoC provides a time-predictable communication system that’s key to distributing the number of cores to safety-related applications. The network provides high throughput while keeping the latency low.

In addition, NoC eXpress (NoCX) interfaces can be used to link multiple chips together in a larger computing array. NoCX is also a way to link the chips to FPGAs and other external coprocessors.

Like numerous other many-core solutions, the MPPA can be programmed using conventional tools such as C and C++ compilers as well as OpenCL. This approach allows developers to use standard libraries like OpenCV and OpenVX. Likewise, its real-time support makes it possible to use operating systems like AUTOSAR.

2. The MPPA Dev 2 is an all-in-one PC-based development station for the Kalray MPPA platform.

Kalray provides a number of MPPA development platforms. The MPPA Dev 2 (Fig. 2) is an all-in-one, PC-based development station. There’s also the MPPA EMB2, a small-form-factor version of the MPPA Dev 2, and the MPPA Box2 embedded prototype platform.

Other many-core processor solutions include Intel’s Xeon Phi and Mellanox’s Tilera. These platforms are being using in non-automotive applications. Kalray’s platform would be applicable to those application areas as well.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: