Analog Devices Eyes Bigger Role in 5G Base Stations With Radio SoC

Telecom giants are buying wireless base stations by the thousands to install in new 5G networks in the U.S., China, Europe, and other regions around the world. But they are still in the early stages of 5G deployments.

Against that backdrop, companies are vying to supply more of the chips at the heart of these base stations. Analog Devices, for its part, is trying to get a larger slice of the market with its first family of 5G radio SoCs.

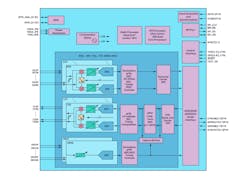

The semiconductor maker said the ADRV9040 is the first in a new series of RadioVerse SoCs. The chip has a wideband RF transceiver with eight transmit and receive channels with 400 MHz of bandwidth and a high dynamic range. The chip also adds on a range of internal accelerators to run digital-signal-processing jobs like digital predistortion (DPD) that usually require the use of a field-programmable gate array (FPGA).

Analog Devices said ADRV9040 stands out by placing everything on a power-sipping system-on-a-chip (SoC). The chip folds in its ZiF radio architecture to simplify RF filtering and other signal-chain components.

“RadioVerse SoCs are designed to optimize the full radio solution rather than just a single component or interface,” said Joe Barry, VP of the wireless communications unit at Analog Devices.

Base Station Boom

Analog Devices already sells many of the critical radio components that go into 4G and 5G base stations, including the RF converters that transform analog signals into digital signals and vice versa in a radio unit.

ADI said the RadioVerse series is also already the most widely used family of software-defined transceivers in 4G and 5G radios in the world, including at telecom equipment giants such as Samsung Electronics.

Base stations—also called the radio access network (RAN)—comprise a set of boxes that are usually mounted on poles or buildings and connect cellphones to a cellular network. A base station consists of several key parts, including the radio unit (RU) that converts and amplifies radio-frequency (RF) signals. The radio is located close to or directly integrated into the antennas.

The RU is connected to a distributed unit (DU) that houses the main baseband processor and handles L2 and L3 signal processing work.

Analog Devices said the chip is suited for small cells, the clusters of short-range base stations deployed in cities, and macro base stations used by telcos for sprawling networks with tens of millions of customers.

Inside 5G Radios

The radio unit houses a range of components, including an RF transceiver IC and digital front end (DFE). The DFE, usually based on an Intel- or Xilinx-designed FPGA, is one of the more critical stages in a base station. It serves as a sort of bridge between the RF transceiver and other analog ICs to the baseband processor on the other side, which is used to handle the PHY (or L1) signal-processing jobs in the radio.

The DFE can reconfigure the channels in the radio in real-time and carry out pre-processing on radio signals as they come in from the base station’s antennas, clarifying and conditioning them to take out interference.

Although it has a wideband RF transceiver at its core, Analog Devices said the RadioVerse SoC can also do many of the pre-processing and pre-conditioning workloads that would previously run on a separate FPGA.

Integrating everything on a single chip keeps the hardware’s heat dissipation in check and saves PCB space. The hardware accelerators under the hood also help the 13-W SoC run more efficiently at the system level.

Power efficiency is one of the most important metrics for 5G radios, said Kevin Mohammed, who works in product marketing for the wireless communication unit at Analog Devices. Power-hungry chips can cause thermal hot spots in the radio that require bulky, heavy heatsinks to keep them cool. Delivering power to a base station is usually one of the largest operating costs in a wireless network, he said.

According to Analog Devices, the chip can handle the harsh temperatures that a base station is subject to out in the field. The chip will function at a maximum junction temperature of 110°C, with operation up to 125°C.

Hardware Acceleration

The hardware accelerators at the heart of the new SoC can run carrier digital upconversion (CDUC) and carrier digital downconversion (CDDC), which convert raw radio or intermediate frequency signals into a baseband signal. The new chip can carry out other signal-processing jobs, like crest-factor reduction (CFR), which reduces peak-to-average noise in radio transmissions, and closed-loop gain control (CLGC). There is a quad-core Arm Cortex-A55 CPU in the SoC to supplement its signal-processing powers.

Integrating a wideband RF transceiver and DSP into a single chip also shrinks the amount of data traveling from the RadioVerse SoC to L1 PHY in the radio, reducing the processing load on the latter.

The serial data interface consists of eight SerDes lanes that support JESD204B and JESD204C standards.

The chip also adds hardware acceleration for digital predistortion technology (DPD), which is widely used to increase the linearity of RF power amplifiers (PAs). Linearity is a power amplifier's ability to block out noise and interference that can scramble RF signals. Linearity usually takes a hit at higher output power levels.

The DPD technology in the new chip means that it can be paired with more energy-efficient PAs, reducing the power consumption of the radio unit in a 5G base station and, as a result, lower costs.

Analog Devices said the ADRV9040 can be paired with many of the most popular types of RF PAs in 4G and 5G base stations, including GaN-based devices with higher power densities.

To wring out more power efficiency at the system level, Analog Devices said it partnered with leading players in the power amplifier market to pre-test the 5G radio processor with more than 50 of their PAs.

Chip Partitioning

Analog Devices is also working with other industry heavyweights to help guarantee its slot in 5G radios. Last year, it partnered with Marvell to roll out a reference design for a 5G massive MIMO radio unit that integrates its wideband RF transceivers with Marvell’s Octeon Fusion family of baseband SoCs. Intel is building out a 5G radio platform that combines its FPGAs with Analog Devices' RF transceivers.

Analog Devices said ADRV9040 can be used in a wide range of configurations and form factors with chips designed by Intel, Marvell, or other partners. The SoC is “not necessarily a single-chip alternative in those designs, rather it optimizes the chip partitioning to enable the most competitive solutions along the dimensions of size, power, weight, and cost,” Mohammed said.

The ADRV9040 works with a new standard for open radio access networks called Open RAN, giving telcos the extra flexibility to mix and match components in a base station and avoid lock-in with a single supplier.

Analog Devices said the ADRV9040, which is currently sampling to early customers, will be available in a 27- × 20-mm, 736-ball, ball-grid-array (BGA) package. The SoC is controlled via an SPI serial port.