Typical system design initially focuses on microcontroller (MCU), CPU, memory, and I/O components and architectures. Later, it focuses on how to supply the various clocks that the system requires. Complicated systems can end up requiring 10 or more clocks.

What is the best way to provide all of those frequencies, given the choice of discrete resonators, crystal oscillators, fan-out buffers, clock generators, and other timing device options? Consolidating the timing needs into silicon clock generator components can reduce board real estate and system costs. But does this approach always make sense?

A Typical System Design

Let’s say you’ve finished the architecture of your system and selected the key components. It interfaces to the real world, so there is at least one amplifier, analog-to-digital converter (ADC) or digital-to-analog converter (DAC), some type of human interface, an MCU and/or DSP, memory, a wireless and/or wired Internet connection, and associated power management (Fig. 1). The simulated power-up and power-down sequences, signal-to-noise ratios, computation speed, memory bandwidth, and power consumption meet spec.

1. Any modern system incorporates multiple subsystems that all have unique and potentially incompatible clocking requirements.

You’re almost ready to go to board layout to simulate the layout parasitics and ensure they don’t disrupt performance. You’re also planning to follow layout guidelines to minimize electromagnetic interference (EMI). It’s difficult to model, though, so you still have your fingers crossed that the system will pass the Federal Communication Commission (FCC) regulatory limits during EMI testing.

System Frequency Plan

One of the final steps before going to layout is selecting the frequency references for all the components. Some of the devices only have a clock-in pin that would require an external oscillator, and some are designed to work with either an external clock or crystal.

Your colleague relates a story about trying to debug a crystal oscillator startup problem at a specific temperature and voltage corner in a previous design. It ultimately turned out to be insufficient crystal oscillator gain when used with a particular crystal and load. You would sure like to avoid that issue!

In addition, the quality assurance team warns against the mechanical unreliability of crystals. You count the frequencies needed, eight in total, one for each of the analog-to-digital, digital-to-analog, MCU, memory, and local-area network (LAN) and wireless LAN (WLAN) components, as well as two for the DSP/system-on-chip (SoC).

If you could generate all of those frequencies from a single clock generator and route them to the various components, you could save a lot of area and component cost, as well as improve reliability by using a single crystal. But will the system still work? Can the clock generator provide the frequency and signal quality needed for each component? And, what other advantages or disadvantages might occur?

If you’ve ever experienced that uncertainty, you’re not alone. All conscientious system designers ask these questions when they’re trying to optimize the frequency generation performance at the lowest total cost including component count, area, manufacturability, and reliability.

While each system is different, consider the following helpful guidelines for making that decision. To understand the tradeoffs in consolidating frequency sources into clock generators, we need to understand the benefits and limitations of alternative sources (Fig. 2).

2: There are different ways to generate clock signals. Understanding their tradeoffs is the first step toward clock management.

Discrete Resonators

Discrete resonators are designed to work in conjunction with a semiconductor gain circuit that is connected to both terminals of the resonator. The output of the gain circuit is initially the amplified noise at its input. The piezoelectric and physical properties of the resonator material allow the vibrating resonator to act as an electronic filter, passing the frequency components in its pass band back to the input of the amplifier. At the pass band frequency where the loop gain is greater than 1 and the phase is 360°, the resonator begins to oscillate, producing a stable frequency source at the amplifier output.

The two most common discrete resonators available are ceramic resonators (typically made of lead-zirconium-titanium or PZT) and quartz crystal resonators (made of silicon dioxide or SiO2). The primary difference is that the ceramic resonators cost less and are much less precise with initial accuracy surpassing 5000 ppm, and they drift significantly with temperature and age (~2000 ppm each in commercial applications). Crystal resonators are more precise, with accuracy of less than 50 ppm inclusive of temperature and aging for AT cut crystals. Certain ASICs designed to vary the capacitance on the pins to control small deviations in frequency (less than ±150 ppm) also use crystal resonators as voltage-controlled crystal oscillators (VCXOs).

One of the major drawbacks of discrete resonators is the effort and development time required to ensure that the gain circuit, resonator, and board layout (all from different manufacturers) are properly matched. The analysis includes verification of reliable startup and accuracy over temperature, process, and voltage. In addition, the analysis needs to ensure that the crystal is not overdriven, which would accelerate aging. The lower amplitude and sinusoidal waveform of the external signal also results in slow signal edges, which makes discrete resonators more sensitive to external noise. The advantages of discrete resonators include excellent close-in phase noise, noise within kilohertz of the resonant frequency, and low power consumption.

Discrete Oscillators

A discrete oscillator combines the semiconductor amplifier mentioned above with a resonator in the same package. A crystal resonator is the most common resonator type, although surface acoustic wave (SAW) resonators and more recently microelectromechanical systems (MEMS) resonators are sometimes used. SAW resonators operate at higher frequencies (greater than 400 MHz)and MEMS resonators provide performance similar to that of a crystal, though they are smaller and more shock resistant.

A key advantage of discrete oscillators is that the amplifier, resonator, and connection capacitance can be matched in the factory to ensure reliable startup and frequency accuracy independent of board layout. Of course this comes at increased component cost, area, and power consumption compared to a discrete resonator. Since most oscillators only generate one frequency, systems requiring multiple frequencies are often better served by consolidating frequencies into one or two clock generators when possible. For a more detailed discussion of discrete resonators and oscillators, visit http://sss-mag.com/pdf/osctut.pdf.

Clock Generators

Clock generators, or frequency generators as they are sometimes called, combine the oscillator with one or more phase locked loops (PLLs), output dividers, and output buffers. In most cases, the resonators are external, but there is a trend in the industry to include the resonators within the clock generator package to eliminate the disadvantages of discrete resonators outlined above.

But even if the resonator is external, the effort required to match resonators, amplifiers, and board layout is greatly reduced since the clock generator only needs one reference to generate all other frequencies. In addition, minimizing the number of discrete resonators will improve system ruggedness and reliability.

The advantages of consolidating frequencies into a clock generator are many. In addition to the reduced crystal matching effort and improved reliability, advanced clock generators typically offer several features that benefit system performance. The output frequency can be changed in real time, which is useful when systems must adapt to various standards around the world (for example, PAL versus NTSC), to accommodate system variations by the end user (for example, attaching different video monitors), or to accommodate bill of materials (BOM) changes used to ensure supply (for example, supporting audio DACs from two suppliers having different sample rates). System clock frequencies also can be varied slightly during system validation or in production testing to ensure sufficient timing margin, and spread spectrum clocking can be employed to reduce the costs of EMI suppression.

There are many different types of clock generators, and each is optimized for different performance and cost targets:

• PLLs based on ring oscillators versus LC oscillators: Ring oscillator PLLs typically provide lower cost, power, and performance while LC oscillator PLLs provide higher performance at the expense of higher cost and power.

• Singled-ended CMOS outputs for minimum power versus differential outputs such as low-voltage positive emitter coupled logic (LVPECL), low-voltage differential signaling (LVDS), and high-speed current steering logic (HCSL) that minimize coupled noise at the expense of higher power consumption.

• Incorporation of automatic gain control on the crystal oscillator to maximize startup gain and then reduce the gain to minimize crystal power dissipation and associated aging versus a lower-cost inverter-based oscillator with an internal or external power limiting resistor.

• Availability of a serial communication interface versus pre-programmed frequencies and pin-selectable functionality.

• A low number of outputs in smaller packages versus a high number of outputs in larger packages.

• Allowing mixed voltage supplies to drive different output voltage levels versus a single supply voltage.

Navigating the wide selection of available clock generators and trying to match them to your system requirements can be a daunting task. As a result, you should work with a clock vendor that offers a large portfolio of available clock generators to ensure an optimum solution. Only a couple of semiconductor companies offer a comprehensive portfolio of clock generators, including Silicon Labs.

Selecting The Right Frequency Sources

The following decision tree will help you narrow the frequency source choices and make an optimum plan for minimizing the frequency sourcing components and associated cost in your system:

• Criteria 1: If your system only requires one or two frequencies of less than 50 MHz, then discrete crystals or oscillators are the lowest-cost solution. If frequencies are greater than 50 MHz, or multiple copies or special control of a frequency is needed, then a fan-out buffer or clock generator would provide a lower-cost solution. Special functions include changing frequency during system operation or test and spread-spectrum technology for EMI reduction.

• Criteria 2: If there are components in your system that will pull the frequency of a discrete crystal, a discrete crystal is your only choice. Make sure you use one recommended by the ASIC vendor or one that matches the detailed crystal parameters they specify.

• Criteria 3: If components in your system require extremely accurate clocks (less than 20 ppm) over temperature and voltage, an external oscillator such as a temperature-controlled crystal oscillator (TCXO) will be required. If your system requires frequencies in addition to one high-accuracy frequency, the TCXO often can be used as the reference to a clock generator to save cost. Care must be taken to match the TCXO signal levels to the clock generator input levels and minimize coupled noise into the primary TCXO signal path.

• Criteria 4: Components that need frequencies with specific phase noise requirements (typically for wireless communication references) will often need to be sourced from a crystal oscillator or LC-based frequency generator. Since lower-cost ring-based clock generators often use a crystal oscillator for the reference, most clock generators output that frequency directly (without going through a PLL) to provide a signal with low phase noise (Fig. 3a). But if the same clock generator is generating multiple outputs with different frequencies, be sure to check the spur content in the reference frequency output spectrum to ensure it does not interfere with or alias to adjacent wireless channels (Fig. 3b). The spur locations will change depending on the combination of generated frequencies. If the spur levels or locations are incompatible with the application, then moving some of the clock generation into a second clock generator may resolve the problem. Otherwise, a discrete resonator or a discrete oscillator is needed.

3. Lower-cost, ring-based clock generators that use a crystal oscillator reference and output that frequency directly may generate spurs (a). A source with a PLL output can exhibit lower phase noise (b).

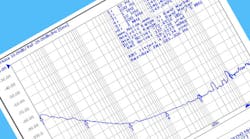

• Criteria 5: A clock generator also can supply components that need reference frequencies with stringent “rms jitter” requirements, which are common in high-speed digital communication systems. Jitter is the uncertainty or error of a clock edge in time relative to a “perfect” clock signal, and rms phase jitter is the integral of phase noise over a specific frequency band (Fig. 4).A very common rms jitter specification originated for SONET data transmission applications, and it is specified at less than 1 ps rms over the 12-kHz to 20-MHz frequency band. Since this standard has been around for a few decades, many semiconductor components specify this as a default jitter limit without actually calculating the true system jitter requirement.

4. Spectra from an LCVCO PLL illustrate degradation in phase jitter with (a) and without (b) additional frequency outputs enabled.

Summary

With multiple sources for frequency generation available, it’s possible to optimize system clocking requirements for the lowest overall cost while retaining excellent system performance (see the table). Some cases only need passive resonators, while in many systems, especially those requiring two or more frequencies, the passive resonators are best replaced by silicon timing devices such as clock generators and fan-out buffers. In addition to reducing frequency generation and EMI suppression costs, silicon frequency generators offer additional capability for BOM consolidation, system configurability, and outgoing test.