Enhanced Circuit Yields Versatile, Efficient Switch-Mode Solenoid/Relay Driver

Download this article in PDF format.

Several years ago, Paul Rako, in collaboration with the late, great Bob Pease, wrote a terrific article about the finer theoretical and practical points of electromagnetic solenoid-driver circuits.1 It noted that most solenoids need less power to sustain actuation after the plunger is pulled in than is needed to actuate them in the first place. Important power saving and heat reduction without loss of mechanical performance are therefore possible if drive voltage starts out high for pull-in, then backs off to a lower value for hold.

Bob’s method for power reduction (see the first figure of Paul’s discussion) was elegantly simple, consisting merely of a resistor and capacitor connected in parallel with each other and in series with the solenoid coil. Transient pull-in power is supplied by the capacitor, while steady-state hold current flows through the resistor, chosen to be 60% to 70% of the resistance of the coil. Hold current is therefore reduced by ~40% and coil heat production is cut by more than 60%. That’s a pretty impressive reduction in solenoid-coil power dissipation. However, that series resistor consumed power, too: 70% as much as the solenoid.

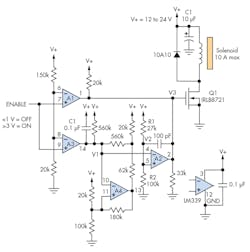

1. This switch-mode solenoid-drive circuit maximizes hold-mode power savings by using comparators to efficiently manage drive waveforms.

The circuit presented here (Fig. 1) takes the same power-reduction principle to the next logical level by eliminating the series voltage-dropping resistor and replacing it with efficient switch-mode. (Note that the design applies to driving relay coils and contactors.)

Driver topology is organized around the four analog comparators that comprise an old “friend,” the LM339 quad IC (A1 through A4) that combine to control a power FET (Q1) in response to the logic-level ENABLE input. Solenoid actuation begins when ENABLE activates A1, turning on Q1 and A2, starting the drive cycle (Fig. 2).

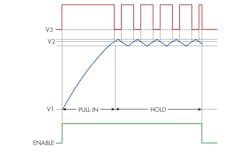

2. The drive-sequence timing controls the solenoid pull-in and subsequent hold operation to conserve power.

The V1 timing ramp generated by A3 rises at a rate determined by C1 (pull-in time Tpull-in = 5 × 105 × C1 = 50 ms for C1 = 0.1 µF) and the associated resistor network, generating the initial full-voltage (V+) PULL-IN pulse V3 at Q1’s gate. This continues until V1 arrives at the V2 threshold of drive modulator A2 (set by R1 and R2), initiating reduced-power HOLD mode. Modulation of V3 and Q1 conduction is driven by the A4 oscillator, which starts up when V1 rises to A4’s threshold, and imposing a triangular ripple in V1. This cyclically switches A2, thereby establishing a ~70% duty factor on Q1’s conduction. Subsequently, it reproduces the hold-mode solenoid power-dissipation savings described in the Pease/Rako article, while avoiding the inefficiency of a voltage-dropping resistor.

The versatility of the resulting driver is enhanced by its ability to accept a power source from 12 to 24 V, and to accommodate solenoid current demand up to 10 A (i.e., up to 240 W), so that this single circuit can serve in a wide variety of solenoid-drive applications. Hold-mode power consumption is reduced by 60%, and overall efficiency easily exceeds 90%. Reset of the C1 timing capacitor takes less than a millisecond.

Steve Woodward has authored over 50 analog-centric circuit designs. A self-proclaimed "certified, card-carrying analog dinosaur," he is a freelance consultant on instrumentation, sensors, and metrology freelance to organizations such as Agilent Technologies, the Jet Propulsion Laboratory, the Woods Hole Oceanographic Institute, Catalyst Semiconductor, Oak Crest Science Institute, and several international universities. With seven patents to his credit, he has written more than 200 professional articles, and has also served as a member of technical staff at the University of North Carolina.

Reference

“What’s All This Solenoid Driver Stuff, Anyhow?”, Electronic Design, August 5, 2013.