The Performance And Power Challenges Of Multi-Antenna Broadband Radio

Cellular network operators seek significant equipment cost reductions as they strive to increase their network coverage and capacity through expanded bandwidth, a growing number of multiple-input multiple-output (MIMO) antennas, more cell sites, and new transmission frequencies. At the same time, they’re pursuing reduced operating costs by acquiring radio equipment that delivers better efficiency and integration.

Manufacturers that provide wireless infrastructure equipment to these network providers seek system-level design solutions that provide greater integration levels, higher performance, and increased flexibility while lowering power consumption and acquisition cost. Equipment manufacturers must achieve all of these goals while shortening time-to-market as well.

With the rollout of TDD-LTE and FDD-LTE underway in many parts of the world, there has been a shift in desired equipment features and performance requirements compared to previous air-interface rollouts. The most common configuration used for the CDMA2000 and WCDMA 3G rollout was a 20-MHz 2x2 radio, but that has long since evolved to configurations that deliver wider bandwidth and support more frequency bands. Manufacturers are now commonly developing MIMO radios capable of delivering as much as 100 MHz of usable bandwidth. These new configurations typically employ 4x4 and 8x8 MIMO antenna arrays.

This file type includes high resolution graphics and schematics when applicable.

Development of these ultra-wideband radios will allow network operators to deploy a single radio that supports multiple frequency bands of interest—for example, 1800 MHz, 1900 MHz, and even 2100 MHz in the future—resulting in fewer remote radios mounted on the tower top, which in turn reduces costs. This evolution not only saves significant capital equipment costs through the use of fewer radios, it also significantly reduces operating costs and site-rental costs through wind-loading reduction and reduced total weight loading on the tower.

A 100-MHz 8x8 radio requires 20 times more signal processing than a 20-MHz 2x2 radio. When considering the digital and analog processing requirements for such radio equipment, it is hard to see how the products could ever be realized while meeting mechanical, thermal, and cost constraints imposed by passively cooled remote radios. Clearly, continued evolution of new generations of digital and analog ICs is required.

In The Field

Consider the system-level requirements for implementing a 100-MHz, 8x8 cellular radio. The dimensions that define the required devices include the number of antennas, the air interface, the number of carriers, and the instantaneous bandwidth. The number of antennas defines the required number of digital-to-analog converter (DAC) and analog-to-digital converter (ADC) connections. The radio’s instantaneous bandwidth defines the sample rate and therefore defines the speed and number of serializer-deserializer (SERDES) ports required to connect the digital signal processing in the system-on-chip (SoC) with the DACs and ADCs.

Data converters have advanced significantly over the last few years with many manufacturers now offering multiple DACs and ADCs within a single package, connected to the digital radio processing circuitry via JESD204B. The JESD204B interface standard replaces the older, previously used low-voltage differential signaling (LVDS) parallel interfaces with high-speed SERDES ports capable of running at 12.5 Gbits/s.

JESD204B interfaces significantly reduce the number of required connections between the DACs and ADCs and the digital front-end processing circuitry. The result is fewer printed-circuit board (PCB) layers and reduced interface power. Furthermore, these JESD204B converters are now becoming even more integrated. They are absorbing entire uplink and downlink RF-processing subsystems, resulting in high-performance RF ICs that include the DACs, ADCs, filtering, and modulators needed to create highly integrated and high-performance analog front ends (AFEs).

In addition to determining the number of required SERDES transceivers, a cellular radio’s bandwidth and antenna count dictate the amount of logic and DSP required for processing algorithms including digital upconversion (DUC) and digital downconversion (DDC). Crest factor reduction (CFR) and digital pre-distortion (DPD), two additional and commonly used algorithms, improve a radio output power amplifier’s efficiency.

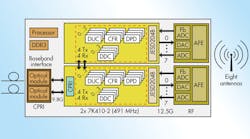

Based on the DSP resources required for implementing wideband radios and the number of SERDES required to communicate with eight antennas, a cost-effective method of implementing a cellular radio using current-generation architectures would be to split the algorithmic processing between two devices (Fig. 1). This system partitioning effectively creates two 4x4 100-MHz radios. It also spreads the operating power evenly across two digital devices, easing the thermal constraints and simplifying the design’s mechanics.

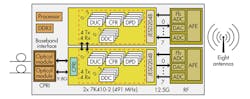

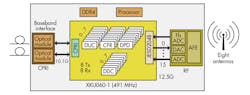

However, this system-level partition is no longer needed using a new breed of devices, such as the Xilinx Kintex UltraScale family, which have significantly more DSP capability and a larger number of SERDES ports while consuming significantly less power.

The Architecture’s Role

To address the new level of challenges, the underlying archirecture must be highly tuned to the needs of this type of radio design. In the UltraScale architecture, highly efficient block RAM and lookup table (LUT) RAM and optimized DSP48E2 DSP blocks efficiently combine to create the many types of filters needed for DUC, DDC, CFR, and DPD signal processing. Using a programmable-logic fabric and on-chip memory allows the implementation of high-performance, soft microprocessors that can be used with hardware acceleration to implement highly scalable, low-footprint coefficient engines for DPD processing.

Time-division multiplexing can be used with some performance-oriented archiectures to further reduce the amount of on-chip area devoted to signal processing while retaining the low power consumption of a programmable radio design. In the case of the Xilinx FPGA, for example, a 100-MHz 8x8 radio can be implemented with just one Kintex UltraScale FPGA (Fig. 2).

To implement such a complex radio in a single device, the overall operating power must drop considerably to reduce the generated heat. Low-power operation can be achieved in several ways. First, a more power-efficient 20-nm device can replace the static power of two 28-nm devices. The device shown in Figure 2 consumes less power than the two shown in Figure 1 while implementing the same number of channels.

Furthermore, careful design has significantly reduced the dynamic power of the devices’ programmable-logic fabric and SERDES transceivers. Fewer DSP blocks are needed for digital filter implementations based on complex multiply/accumulate (MAC) operations. Reducing the required number of DSP blocks reduces the dynamic power and area needed to implement DUC, DDC, CFR, and DPD algorithms.

Approaches such as these can reduce the system-level cost by as much as 8% per transmit/receive pair and power by more than 31% relative to an implementation based on a previous-generation device. Additional system-level cost savings can be realized through the reduced number of required PCB layers and reduced power supply complexity. A smaller power supply and smaller, less complex cooling hardware further reduce the remote radio system’s weight and the required enclosure size, which additionally cuts bill-of-materials (BOM) and operating costs.

Summary

Network operators demand increasingly capable, low-cost radio infrastructure equipment with low operating power and high reliability. Integration is the key to achieving all of these objectives. Emerging ultra-wideband MIMO radios that could only be implemented using multiple devices that consume extra board space and more operating power now can be more efficiently implemented in high-performance, low-power, and highly integrated architectures, including those that form a new class of FPGA device families.

David Hawke is the director of wireless product marketing at Xilinx Inc., focusing on basestation products in the company’s Communications Business Unit. He has more than 20 years of experience in the semiconductor industry in roles including design, application engineering, sales, and marketing. Prior to transferring to marketing from technical sales in 2005, he was a senior staff field application engineer covering the wireless market sector in the U.K. for seven years. He has been published in a number of trade journals and spoken at conferences and industry evens such as LTE World Summit, Wireless China, Next Generation Networks, and IWPC conferences. He began his career in design at Rutherford Appleton Laboratory, the U.K. He holds a B.Eng in electronics from De Montfort University, Leicester, U.K. He can be reached at [email protected].