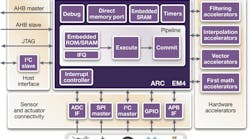

The DesignWare sensor IP subsystem from Synopsys is a complete and integrated hardware and software solution for sensor control applications. Optimized to process data efficiently from digital and analog sensors with ultra-low power, the fully configurable subsystem consists of the DesignWare ARC EM4 32-bit processor, digital interfaces, ADCs, hardware accelerators, a comprehensive software library of DSP functions and software I/O drivers. The subsystem provides a complete and pre-verified solution meeting the requirements of applications such as smart sensors, sensor fusion and sensor hub. Included with the power- and area-efficient ARC EM4 32-bit processor core are custom extensions and instructions supporting application-specific hardware accelerators and tightly integrated peripherals. Multiple configurable GPIO, SPI and I2C digital interfaces are included for off-chip sensor connections as well as ARM AMBA AHBTM and APBTM protocol system interfaces. The analog interfaces include low-power high-resolution ADCs that efficiently digitize sensor data for the processor. The subsystem’s HAPS FPGA-based prototyping solution enables immediate software development and provides a scalable platform for full system integration and validation. The DesignWare sensor IP subsystem is targeted for availability in October 2013 to early adopters, with general availability planned for Q4 2013.

Comments