This file type includes high resolution graphics and schematics when applicable.

At any given time in the electronics industry, thousands of product areas and new technologies are in development. No one person can keep track of them all, but the major publications and Web sites do a remarkably good job overall. Every once in a while, it helps to step back a bit and look for the industry trends behind many of the specific development projects underway. This is a useful way to cut through some of the clutter, make investment decisions, search for promising employment opportunities, or choose new career paths.

When such trends exist, they’re also reflected both in press coverage and in technical papers in journals and at conferences. Next week, the Design and Verification Conference (DVCon) India will be held September 10-11 in Bangalore. Its technical program of more than 70 talks, tutorials, keynotes, panels, and posters covers a wide range of topics. This article highlights five current trends in the electronics industry and connects them to some of the hottest sessions at DVCon India.

UVM Extensions

One clear trend within the verification space is the need for extensions to the well-established Universal Verification Methodology (UVM). An Accellera standard that was recently handed off to the IEEE, the UVM defines how to build reusable testbench components for simulation. It has been remarkably successful at verifying blocks and subsystems, automating sequence generation, and largely replacing handcrafted test vectors. However, the UVM cannot be all things to all engineers, and some cracks are starting to show.

Many companies have extended the UVM to languages beyond the original SystemVerilog, to system-level verification beyond the original target of RTL, to hardware platforms beyond the original focus on simulation, and to verification of chips with analog/mixed-signal (AMS) content. The DVCon India technical program includes more than a dozen talks and posters related to effective use of the UVM as it is currently standardized, and ideas for future revisions and extensions.

ESL Gaining More Traction

The second trend is the slow but steady move toward electronic-system-level (ESL) design and verification. One of the reasons this trend is hard to track is that ESL means many things to many different people. The design side usually focuses on describing the chip in SystemC and using high-level synthesis (HLS) to map to RTL and gates. Commercial solutions for HLS have been in place for more than a decade, yet the technology has yet to become mainstream. But adoption continues to grow every year, so it is part of the ESL trend.

On the verification side, ESL mostly refers to high-level modeling of a system or SoC in a virtual platform. The level of detail is enough to run software, estimate power consumption, and measure performance metrics, but not enough to run HLS. There’s much speculation (and some actual research) about whether a single model can suffice for virtual platforms and synthesis. In the meantime, the virtual model is often written in SystemC so that it can be transformed into the HLS source by a series of successive refinements introducing more design details.

DVCon India offers a track specifically for ESL, running in parallel with the Design and Verification (DV) track. More than 20 talks and posters cover many aspects of system-level architecture, design, and verification. There’s a noteworthy focus on the both SystemC and the transaction-level modeling (TLM) standards, which are widely used in the ESL space. One talk even goes beyond hardware verification to address pre-silicon testing of driver software.

Multi-Everything

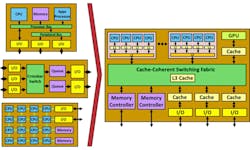

In the architecture space, many types of chips are progressing toward multiprocessor system-on-chip (SoC) designs with multiple memories and multi-level caches. Such convergence is resulting in a common architectural style that depends heavily on embedded software content to differentiate the end application and product (Fig. 1). This trend is happening due a series of sub-trends in chip architecture:

• Large chips are adding embedded processors to implement complex functionality while retaining flexibility.

• Single-processor chips are adding multiprocessor clusters to get better performance at a given process node.

• Multiprocessor chips are using shared memory for effective data transfer and inter-process communication.

• Neighbor-connected processor arrays are moving to shared memory to reduce cross-chip data latency

• Multiprocessor designs are adding caches to reduce memory access time and bypass memory bottlenecks.

• Multiprocessors with caches require coherency to ensure that the right data is always accessed.

Since embedded software is so central to this style of chip, it becomes very difficult to verify the design using a traditional simulation testbench. It is preferable to run test cases on the embedded processors in simulation, and beyond, through emulation, FPGA prototypes, and even actual silicon in the lab. UVM provides no facility for linking code running on SoC processors with a testbench, so once again the need arises for an extension or new approach. But since UVM works so well on blocks and subsystems, any new method must link to existing testbenches as much as possible.

Portable Stimulus

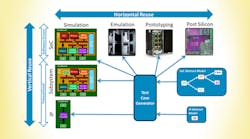

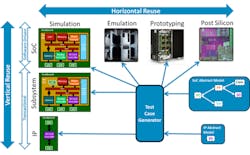

These requirements are driving the fourth industry trend: the search for a portable stimulus solution. The goal is to have a single source for abstract verification specification, and some sort of automatic generation of test cases tuned for specific targets (Fig. 2). This enables vertical reuse, from IP block to full SoC, and horizontal reuse, from ESL and RTL simulations to silicon. This is such a critical need in the electronics industry that the Accellera Systems Initiative has formed the Portable Stimulus Working Group to develop a standard in this area.

Portable stimulus was a hot topic at last year’s inaugural DVCon India show, and will be so again this year. In fact, two tutorials are dedicated to this trend, along with a session devoted to papers on graph-based verification, software-driven verification, automated coverage closure, and other technologies that are keys to a robust portable stimulus solution. All four trends discussed so far come together at this point—thus, a portable stimulus standard:

• Might be viewed as an extension of the UVM.

• Must provide connections to existing UVM testbenches.

• Must support high-level ESL simulations as well as RTL.

• Must generate code to run on embedded processors.

• Must support test cases running on many-core SoCs.

Impact of IoT

The final trend is probably the most obvious since it’s discussed all the time in the trade press: the predicted exponential growth of the Internet of Things (IoT). Many feel that this area has been hyped beyond all rationality and that too many disparate technologies are being gathered under the IoT banner. However, it is quite clear that a large market exists for network-connected devices of all kinds, and it will very likely continue to grow at a rapid pace. Many new consumer and business applications are seemingly being proposed every day.

Most IoT devices will have to be small and inexpensive, which would seem to place a lower design and verification burden on the chip projects. However, many will need to run on extremely low power and some will be in locations difficult to access for repair or upgrade. Virtually all IoT services will be SoCs, with embedded software providing part of their product differentiation. Although some may not need multicore or many-core capabilities, the wide availability of these platforms may mean that they will be selected anyway.

Many of the DVCon India sessions related to the first four trends will also be applicable to those engineers designing and verifying IoT products. The show also includes a panel discussion specifically on the challenges of IoT verification. As noted, low power consumption will be a requirement for nearly all IoT designs; three talks are related to this topic alone. Finally, most IoT devices will have analog sensor interfaces, so talks on AMS and PHY (physical layer) verification will also be of interest.

Over the next few years, much energy will be devoted to address these five trends: UVM extensions, ESL development, many-core designs, portable stimulus, and IoT products. Engineers involved in any of these areas will want to benefit from all available information from the trade press, technical journals, and industry conferences. Lots of very smart people face similar problems, so there’s much to be gained in the industry by sharing ideas and results whenever possible.

Tom Anderson has more than 15 years of experience in EDA verification applications and marketing. He has served as Product Management Group Director for Advanced Verification Solutions at Cadence, Technical Marketing Director in the Verification Group at Synopsys and Vice President of Applications Engineering at 0-In Design Automation. Before moving into EDA he was Vice President of Engineering at IP pioneer Virtual Chips, following roles in ASIC design and management. Tom has presented more than 100 conference talks, published more than 200 papers and articles, and contributed to 12 books. He holds a BS in computer systems engineering from the University of Massachusetts at Amherst and an MS in electrical engineering and computer Science from the Massachusetts Institute of Technology (MIT).