It’s time to put to rest 11 of the most common myths about verification intellectual property (VIP). SmartDV’s Bipul Talukdar, Director of Applications Engineering, explains why it’s used in a verification environment to improve debug, coverage closure, and quality; accelerate project delivery; increase return on investment; and reduce the risk of silicon re-spin.

1. Verification IP is an optional part of the verification flow.

Verifying the functional correctness of complex system-on-chip (SoC) designs filled with integrated blocks of IP, many based on complicated industry-standard interface protocols, is a difficult task. That’s why verification teams implement Verification IP in their verification strategy and consider it a key component of the verification flow. It ensures debug, coverage closure, and quality are improved, and project schedules are reduced. It creates an infrastructure for industry-standard interface and interconnect protocol support and offers a known reference to compare with the design under test/verification (DUT).

2. Instead of streamlining coverage-driven verification, VIP complicates it.

Verification is complicated no matter what tool is used, and it consumes an estimated 60-80% of a project’s resources. A testbench for a complex SoC requires a variety of Verification IP to verify system-level functionality and validate target performance by generating application-specific traffic and checkers.

The use of quality VIP removes the requirement for the designer to become an expert on multiple protocols. The VIP does the “heavy lifting” of verifying the design against the details of the protocol specification. It generates comprehensive tests that stimulate and verify different interfaces and standard bus protocols, shortening SoC verification and increasing test coverage. It includes transactions/sequences, drivers, configuration components, a test plan for a specific interface, and test suites to connect to a DUT inside the testbench to simulate or emulate an IP or SoC design.

VIP comes as industry-standard-compliant, plug-and-play modules that verify system-level functionality and validate target performance by generating application-specific traffic.

3. Verification IP is just another verification methodology.

VIP isn’t a verification methodology. It’s unlike either the universal verification methodology (UVM), an Accellera interoperability standard for building testbenches, or the Open Verification Methodology (OVM), a methodology and block library. Verification IP is a valuable component implemented in an available standard verification methodology such as UVM.

4. Verification IP often isn’t compatible with verification languages and methodologies, nor is it platform-independent or reusable.

VIP consists of libraries of reusable verification components and pre-defined functional blocks that

create an infrastructure to support industry-standard interfaces, hardware-verification languages (HVLs) SystemVerilog and SystemC, and methodologies such as UVM. Quality VIP is platform-independent and created to work across all methodologies and languages.

5. Verification IP isn’t portable across verification platforms such as simulation and emulation.

Yes, some VIP is targeted to one simulation and/or emulation platform rather than all commercial platforms.

Transitions from simulation to emulation can be difficult, time-consuming, and resource-intensive. However, some vendors provide platform-independent VIP that works with a coverage-driven verification flow seamlessly across different platforms, including simulation, emulation, FPGA prototyping, and formal verification.

6. VIP is an incomplete solution. The verification group needs to build on additional capabilities.

Verification IP blocks for emulation and FFGA prototyping come as synthesizable register-transfer-level (RTL) code with full API compatibility to move designs from simulation to emulation. These VIP blocks are built-in intelligent debuggers, offering fast compile and system-level simulation run times and fast firmware/software development. The infrastructure framework or testbench comes with stimulus generators, monitors, scoreboards/checkers, and functional coverage models.

7. It’s difficult to find Verification IP for new or revised protocols.

It can be a challenge to find VIP that supports new or revised protocols or open standards, or that addresses the entire verification flow. New or customized VIP development takes time and may not be portable between verification platforms. Specialized compilers that can rapidly create new VIP or customize existing VIP help to cut the time required to introduce new VIP or incrementally customize an existing VIP.

8. Verification IP is slow to compile.

Some but not all VIP can be slow to compile, while others may only target specific verification languages and methodologies and aren’t compatible with others. Platform independence and reusability can be concerns as well. One common complaint is the difficulty verification engineers have analyzing and debugging results. Also, handwritten VIP may not maintain an equal level of performance, efficiency of production, ease of debug ability, and readability.

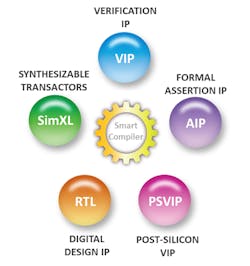

One third-party VIP vendor uses a smart compiler to create verification IP for a range of verification tasks, including formal assertions and synthesizable transactors, post-silicon and design IP, and (not pictured) test suites and documentation. (Source: SmartDV)

Verification IP written at a higher level of abstraction that uses a smart compiler/generator (see figure) to produce the final deployable version of the VIP can prove to be the exception against these complaints. Machine-generated VIP can maintain code quality and linting at a prescribed level to efficiently compile and execute. Such VIP can complement today’s evolving hardware design methodology that generates RTL code from a higher level of abstraction-coded design specification.

9. Not all Verification IP is fully production-worthy and documentation isn’t comprehensive.

VIP often is provided by third-party vendors who are active in interface standards development organizations for networking, storage, automotive, bus, MIPI, and display protocols. They can have an advantage over in-house resources because they verify the correct functionality and compliance with the industry standard.

However, verification engineers must research and evaluate VIP from third-party vendors. They need to understand the technical support for VIP usage and customization, if required. Support can be inconsistent, and customization can be costly and time-consuming. Another important aspect of the evaluation process is to be sure the third-party VIP solution is fully compatible with the standard and addresses the entire verification flow.

10. Transitions from simulation to hardware acceleration are difficult, time-consuming, and resource-intensive.

No cohesive Verification IP solution addresses the entire verification flow. In fact, different verification IP is needed for different steps in the process; there are often gaps in the type of verification coverage offered by a VIP. For example, VIP for simulation may exist without a good solution for emulation, formal assertion verification, and/or even post-silicon verification. Dedicated VIP vendors can fill in the gaps.

One popular myth proposes that the best source for VIP is from the same vendor that provides simulation and emulation platforms. This may or may not be true. The primary business of these vendors typically focuses on software and hardware sales required to build the verification environment. While VIP is offered, it’s not the core focus. Instead, it’s an investment made to support selling the more expensive software and hardware platforms. Vendors that focus on developing and licensing VIP often have broader offerings and better support.

11. Test suite availability for a delivered VIP can be limited.

Creating test suites to cover 100% of a protocol can be a daunting job due to the range of scenarios that tests need to cover and the number of tests that need to be produced. Such a task can be a burden for VIP providers whose main business isn’t to create VIP, but rather to create VIP as enabling solutions for their tools. This isn’t true for companies specializing in the production of VIP. They are experts and machined the process to produce required test suites for 100% protocol coverage paired with the required documentation.