Multi-Die Systems Set the Stage for Innovation

This video is part of the TechXchange: Chiplets - Electronic Design Automation Insights.

What you’ll learn:

- Where the industry is headed with multi-die packaging.

- How Synopsys is supporting multi-die packaging technology.

Abhijeet Chakraborty, Vice President of Engineering at Synopsys, presented one of the keynote speeches at the 2024 Chiplet Summit (watch the video above).

Mr. Chakraborty noted that 2023 was an inflection point for multi-die systems in the semiconductor industry (Fig. 1). Companies, like Synopsys, are providing the tools to design chiplet-based solutions, which is one of the hotter multi-die packaging approaches now available from various fabs.

Some companies, such as AMD, Intel, and NVIDIA, are delivering systems using multi-die technology, usually on high-end platforms that utilize chiplets like high bandwidth memory (HBM). Or they’re tying together different chip technologies like SERDES and analog to high-performance compute systems like FPGAs.

Much of the existing multi-die solutions have been custom, for example, Intel’s Embedded Multi-Die Interconnect Bridge (EMIB). However, standards like Universal Chiplet Interconnect Express (UCIe) and the Open Compute Project’s Bunch of Wires PHY specification are opening up chiplet technology to a wider array of companies and developers. Though the concept of a “chiplet app store” is still a long way away, the availability of more standards-based chiplets is closer at hand.

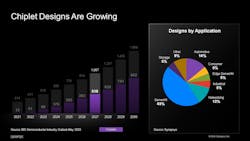

The chiplet and multi-die system market is ramping up (Fig. 2), with a significant portion dominated by server/AI applications being driven by hyperscalers. Automotive represents a sizable chunk, as the approach allows for mixing of chiplet technology in an area where chip customization has significant benefits.

Check out more videos/articles in the TechXchange: Chiplets - Electronic Design Automation Insights.