Using AI to Design FPGA-Based Solutions

What you’ll learn

- What’s new in Xilinx’s FPGA design tool?

- How machine learning is employed by the design tool.

- What’s the difference between using AI in the tool and creating a solution that uses AI?

Xilinx takes artificial intelligence and machine learning (AI/ML) very seriously. It’s been providing optimized hardware platforms to create solutions that utilize AI/ML models, but now the company is using these techniques to improve the FPGA development tools themselves. The new Vivado ML Editions incorporate a number of models in different parts of the software to improve overall system performance and efficiency (Fig. 1).

Another feature in the new version is hierarchical system design with reconfigurable modules. While the system is online, modules can be loaded in milliseconds, allowing for dynamic reconfiguration in the field. ML helps here as well with improved compile times, averaging a five-fold increase in performance up to a factor of 17 for some projects. The ability to process the hierarchy in parallel also improves the design cycle. A team-based graphical IP design flow uses a block-design container-based approach.

Some of the enhancements are incorporated in what Xilinx calls intelligent design runs (IDR). A number of different ML models are used to improve timing closure. Software does the recommendations automatically (Fig. 2).

IDR can reduce the number of iterations that need to be run to find a useful timing closure (Fig. 3). This reduces the overall time to find a solution. The average quality of results (QoR) gain for projects that were evaluated by Xilinx was 10%, with some improving to over 50%.

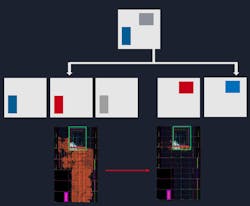

Another aspect of the hierarchical design approach is the ability to modularize designs; therefore, third parties can deliver their IP in a protected fashion while speeding up the user’s customization (Fig. 4). Essentially one or more areas are open for a customer to add its IP to a third party’s design that’s fixed and already debugged. Vivado ML knows what interfaces are provided and enables any design to be included within the restrictions imposed by the base design. This also has the effect of speeding up the customer’s design process, because the fixed area needn’t be recompiled each time. Only the changes are processed.

Vivado ML works with Xilinx’s Vitis software framework support. Vivado ML Editions include an Enterprise Edition and a free Standard Edition. The latter has limited device support but the same functionality as the Enterprise Edition.