Secure FPGA RISC-V SoC Forgoes Heatsink

What you’ll learn:

- How a cool FPGA needs so little power.

- The importance of a smaller RISC-V SoC FPGA.

- What the PolarFire SoC means to RISC-V developers.

- Why security and reliability are key to PolarFire’s success.

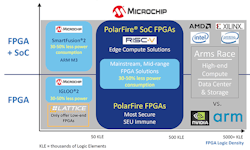

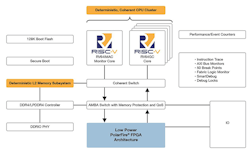

Very-low-power FPGAs have been around for a while, but often there’s the need for those that can handle high-speed serial interfaces like PCI Express or incorporate hard-core processors. Microchip’s latest PolarFire release actually fills out the lower end with a 50K logic elements (LE) and an SoC version with 25K LE that has the same five-core, RISC-V processor complex as the higher-end PolarFire SoC family (Fig. 1).

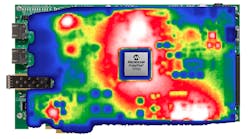

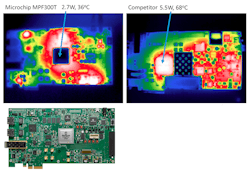

The new, smaller solution can cut power consumption by 30% to 50%—from a family that’s already lower power than its competitors. Thus, these FPGA solutions can run without the need for a heatsink (Fig. 2). Microchip estimates that it costs $1.50/W to dissipate heat, including additions like fans and heatsinks, employing a cold wall in the design, or adding thicker traces on a PCB to redistribute heat. This does put low power parts in perspective when it comes to cost reduction.

The PolarFire FPGA family includes 12.7-Gb/s transceivers and multiple PCI Express (PCIe) Gen 2 endpoint/root ports. It’s also possible to use additional interface ports for high-speed interfaces such as Ethernet using FPGA logic. These types of high-speed interfaces are common in high-end FPGAs but less so in FPGAs with a lower LE count.

The smaller PolarFire FPGA and SoCs are pin-compatible with larger Microchip devices, providing an upgrade path. The FPGA and SoC versions fit into an 11- × 11-mm package. The FPFS025T 25K LE SoC does have a change to address the more limited pin count—a 16-bit DDR memory interface versus the 32-bit version found in the higher-end PolarFire SoCs.

Soft or Hard RISC-V

Microchip has been a RISC-V advocate even as it supports a range of other microcontroller and microprocessor architectures. RISC-V is essentially just a configurable, instruction set architecture (ISA). The implementation supports the ISA, but implementations can vary with different performance characteristics such as silicon footprint, performance, or power.

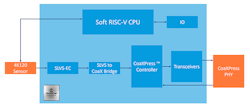

RISC-V can be implemented in an FPGA; Microchip’s development software supports soft-core RISC-V configurations (Fig. 3). Even the smallest PolarFire SoC can handle a RISC-V core with space left for additional logic.

The PolarFire SoC uses a standard RISC-V subsystem regardless of the FPGA logic capacity. The MPFS025T is just the smallest currently available. However, though the same chip package provides a single soft core in all FPGA solutions, there are five RISC-V cores in the subsystem. One manages the system while four cores provide a solution that can run operating systems like Linux (Fig. 4). The system supports secure boot and includes a 128-kB boot flash memory plus a DDR memory control for off-chip storage.

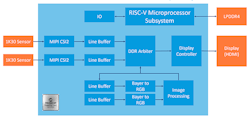

Higher-end PolarFire SoCs offer a larger FPGA fabric, but the 25K LE is sufficient to support complex systems like those with dual 1080p imaging devices (Fig. 5). Of course, in this case, the hard logic for high-speed serial devices allows more of the FPGA fabric to be used for custom logic.

Addressing AI

Machine learning and artificial intelligence (ML/AI) have been ubiquitous in computing solutions from automotive sensor integration to converting streaming video. Therefore, it’s not surprising the Microchip’s FPGA support addresses this aspect of hardware/software.

The VectorBlox Accelerator SDK is Microchip’s software-development solution that handles all PolarFire FPGAs. The SDK is based on OpenVINO. It supports most common frameworks including TensorFlow, Caffe, MxNet, PyTorch, and DarkNet. The FPGA’s math/DSP block dot-product mode has been optimized for ML/AI applications that employ 8-bit inference weights.

FPGA/RISC-V integration excels with ML/AI optimization. FPGA implementations tend to be more efficient than software solutions. They can integrate directly with data going in or out of the chip, or the processor complex, because the additional logic provided by the FPGA can massage the data.

Security and Reliability

Neutron-induced, single-event upsets (SEUs) can really ruin your day by flipping a bit that may cause a catastrophe. SEUs happen all the time, but flipping a bit in a multimedia stream results in an undetectable blip. Unfortunately, a flipped bit in other logic or program code can lead to more significant problems. Microchip’s antifuse flash-based approach is more resistant to SEU problems than RAM-based FPGAs.

Microchip also includes error-correction-code (ECC) support on its block RAM. This is a transparent fix for single-bit errors as well as detecting multibit errors.

The secure-boot support for the processors is augmented with a crypto processor hardened against differential-power-analysis (DPA) attacks. The chips have other forms of anti-tamper support as well. As a result, they can be used in demanding applications that require defense-grade security.

The new Libero 2021.2 software tools support the PolarFire family and other Microchip FPGA solutions. The RISC-V software support is available from a number of vendors, including AdaCore, IAR, Green Hills Software, Siemens/Mentor, and Wind River.