Intel Bets on Advanced Packaging to Help Put It Back on Top

For the first time in decades, Intel is playing from behind in the race to cram smaller and smaller transistors on squares of silicon. But the semiconductor giant recently rolled out one of its most ambitious product roadmaps in years, with a wide range of new technologies that it contends will close the performance gap with TSMC and other foundry rivals by 2024 and push it to the front of the pack in state-of-the-art process technology by 2025.

But to catch up with competitors and lure clients to its new foundry business, the Santa Clara, California-based company is also banking on advances in its advanced packaging arsenal. Intel has started assembling more of its chips out of smaller silicon die that Intel calls tiles, mixing and matching different types of IP, often on different process nodes and even from different foundries, in a system-in-package (SiP) instead of manufactured on a single system-on-a-chip (SoC).

Intel revealed more of its advanced packaging playbook at its Intel Accelerated event last month and introduced two new 3D chip stacking technologies—Foveros Direct and Foveros Omni—both of which will be ready for mass production by 2023.

Slicing chips into smaller building blocks allows Intel to reassemble them in a package that saves more space than cramming them all on a circuit board and is more economical than putting them all on an SoC. It also gives Intel other ways to improve its chips' performance, power, cost, and other properties even as it falls behind on Moore's Law. These modular tiles can also be swapped out or rearranged to meet specific customers' needs.

The freedom to combine different tiles based on the process technology best suited to them is another lure of advanced packaging. For example, the most advanced process, such as the 7-nm or 5-nm nodes, can be used where it counts—in the compute tiles—while more economical legacy nodes, such as 28-nm, can be employed for other chiplets in the system—such as memory and I/O—where smaller transistors can actually hurt performance.

Intel is banking on advances in its core packaging technologies—EMIB and Foveros—to keep it ahead in the race for advanced packaging, where TSMC and other foes are also investing aggressively. It is also hoping to win over customers to its contract chip-making business by opening its 2.5D and 3D packaging technologies as a service, even though many of those customers will probably not use Intel to build their most advanced processor tiles.

EMIB Today

EMIB, which stands for embedded multi-die interconnect bridge, was Intel's first foray into the world of advanced packaging. EMIB is used to connect silicon die over short distances on the same horizontal plane in the package.

For years, if companies wanted to embed heterogeneous die onto a single package for maximum performance, they placed the die on a large, rectangular plate of silicon or "interposer" with silicon wires called vias woven through it. These wires carry signals and power from the substrate, which forms the package’s base, to the die on top of it. With EMIB, Intel uses tiny slivers of silicon called “bridges” embedded in the substrate to connect die in such a way that they act as though they all share the same die—without the restrictions imposed by interposers.

According to Intel, interconnects can be packed together more tightly in a silicon bridge than the wires in silicon interposers or other types of so-called 2.5D packaging, giving it a high-density, high-speed die-to-die connection. The other advantage of EMIB is that it is a lot less expensive than interposers, which are manufactured as single slabs of silicon and are vulnerable to the same imperfections that impact the yields of large SoCs.

EMIB is at the heart of Intel’s Stratix 10 FPGA, which contains a high-performance programmable compute tile surrounded by high-bandwidth memory (HBM) DRAM and high-speed transceiver tiles all in the same package.

The semiconductor tiles connect to the substrate and the silicon bridge inside it with tiny copper pads capped in solder called "micro bumps." These facilitate short, fast electrical connections to the bridge chip embedded in the substrate. The space separating the bumps is called the interconnect pitch. The smaller the bump pitch, the more interconnects Intel can attach to the underbelly of the die. According to Intel, that allows the die to connect to the silicon bridge—and as a consequence, any of the die surrounding it—at higher bandwidths and with less latency.

EMIB Tomorrow

Intel is also expanding EMIB to some of its flagship CPU products, starting in 2022. Intel said its latest family of server processors, code-named "Sapphire Rapids," will be the first in its family of Xeon CPUs to use EMIB, linking four compute tiles based on its new Golden Cove performance core via silicon bridge. Intel said it would also be a “dual-reticle" processor, delivering almost the same performance as a monolithic die based on the same node.

Intel said it could also use EMIB and other technologies to cram more transistors in a single package than it can manufacture at once on a single slab of silicon. Due to the constraints of today's state-of-the-art semiconductor tools, it is only possible to fit transistors within a maximum area measuring around 800 square millimeters. But Intel said that EMIB allows it to get around the upper limit of its production process–also called its “reticle limit.”

Intel said Sapphire Rapids will combine four 400 mm2 compute tiles via EMIB, for a total die area of 1,600 mm2. Intel said that SKUs without HBM will contain 10 EMIB connections in a 78- x 57-mm package.

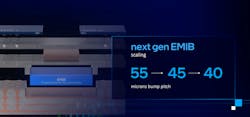

Intel said it is also increasing the density of interconnects in its EMIB technology. The company said the future generation of EMIB scales the pitch of the interconnects from 55-um to 45-um. Further in the future, Intel plans to scale the bumps to 40-um, which would allow the silicon die to transfer data to each other at faster data rates via EMIB. In contrast, the copper bumps in a standard organic package are only around 100-um apart, Intel said.

Ann Kelleher, Intel's senior vice president and general manager of technology development, said that it is also using the 45-um EMIB on a 92- x 92-mm package that will be the world’s largest ball grid array (BGA) package.

3D Foveros

The other pillar of its advanced packaging arsenal is Foveros, which is used to stack silicon dies on top of each other face-to-face, using tightly-spaced copper bumps to cram more performance in a smaller area than EMIB. Power efficiency is another priority Intel is addressing with its 3D Foveros technology. By stacking active silicon in three dimensions, Foveros closes the distance between dies, which leads to higher bandwidth and reduced latency. Another result is that it takes less power to deliver data and power up, down, and around the final chip.

One of the key advantages of Foveros and EMIB is that it lets Intel use best-in-class production, whether from its internal fabs or outside contract manufacturers, for different tiles depending on what it needs. The company has previously said it plans to expand its relationships with many of the world's foundries, including TSMC, Samsung, and GlobalFoundries, as it builds more of the products at the core of its portfolio out of all the disaggregated die.

There are economic advantages as well. For example, these interchangeable tiles are generally significantly smaller than all-in-one monolithic chips, leaving less room for imperfections that can reduce the yield and increase costs.

Intel rolled out its first Foveros-based CPU for personal computers, code-named Lakefield, which incorporated a central compute tile based on its 10-nm node bonded on a secondary IO die manufactured at 22-nm. The chips are connected together with copper bumps that are only 55-um apart and supply power and signals between the floors of the silicon skyscraper. Finally, Intel placed a memory die manufactured external on top of the stack.

Through-silicon vias, or TSVs, are used to connect the base die to the underlying substrate. These wires supply signals and power to the compute tiles above, serving as a freight elevator system in Foveros packages.

Intel plans to use the second generation of Foveros in its “Meteor Lake” CPU generation for personal computers, which will be assembled out of compute tiles based on the Intel 4 process when it comes out in 2023. Intel said Meteor Lake is set to become its second Foveros-based CPU for the PC market after Lakefield. Intel said it would integrate compute tiles, including some supporting tiles manufactured at TSMC, based on a range of process nodes, bonded together by bumps 36-um apart.

Other products in the pipeline use a combination of EMIB and Foveros—called Co-EMIB—to bring more flexibility into the fold. For example, Intel said that it would use Co-EMIB in its first discrete GPU for the data center, code-named Ponte Vecchio. The server chip is a metropolis of silicon, packing more than 40 heterogeneous die—with compute tiles on TSMC's 5-nm node and base tiles on the Intel 7 node—and a total of over 100 billion transistors.

Intel is aiming to push the envelope even further with its new Foveros Omni and Foveros Direct technologies.

Foveros Omni

Foveros Omni is the new name for Intel's omnidirectional interconnect, which increases the flexibility of Foveros by allowing dies to communicate with other dies in the package in any direction—side-by-side, similar to EMIB, or face-to-face, similar to Foveros.

With its Lakefield, Intel was forced to fit the compute die at the top of the package within the confines of the die directly underneath it. But Foveros Omni allows the top die to hang over the side of the base silicon die. Copper columns are then erected from the substrate in the package to the edge of the top die. That allows power to be delivered directly to the top die, routing it around the interconnects carrying signals through the base chiplet.

Intel said that improves signal routing between different floors of the chip and, as a result, its total performance. In addition, the copper pillars piping power to the top die are larger than standard TSVs that run through the base die in its latest generation of Foveros, limiting resistance and resulting in more robust power delivery to the most vital parts of the chip. Intel said Omni also leaves more room for active transistors by replacing many of the vias.

By routing the power around the base die instead of through it, Intel said Foveros Omni opens the door to smaller interconnect bumps. Intel said that Omni would allow for copper bumps that are only 25-um apart. That improves density to 1,600 interconnects per square millimeter of silicon at the same power as its second generation of Foveros, said Babak Sabi, senior vice president in charge of advanced packaging, assembly, and test at Intel.

TSMC and other companies have 3D chip stacking technology (TSMC's SoIC technology, for instance) that takes on Foveros. But the freedom to connect dies vertically or horizontally and stack larger dies on top of smaller ones may give Intel the edge in layout flexibility.

With standard Foveros, it is possible to integrate a wide range of tiles on top of a larger base die. But with Foveros Omni, according to Intel, several tiles can be integrated as base dies in the package. The die can have different footprints and use different process nodes.

Intel said Foveros Omni would be ready for production use by 2023.

Foveros Direct

While Foveros fits more transistors—and thus, more performance—in a smaller area, that also means the power density of the device is increased. Unfortunately, that causes the device to run at higher temperatures, and the heat released in the process can sap the processor's power efficiency. The problem is that all the copper bumps on the bottom of the semiconductor tiles are covered in solder, which adds to the interconnects' resistance and impedes current.

Intel is trying to address that trade-off with its latest Foveros Direct technology, which serves to permanently bond one chip’s copper pads to another's without using bumps capped in solder. Intel said Foveros Direct is a copper-to-copper or hybrid bonding technology that helps improve power efficiency, transistor density, and connection pitch of Foveros chips while limiting heat. Intel said it "blurs the boundary" between where the wafer ends and the packaging begins.

Intel said Foveros Direct allows it to place interconnect wires only 10-um apart on a die, increasing density by an order of magnitude (more than 10,000 interconnects per mm2) over its Foveros Omni technology. Intel said that it also has the advantage of reducing parasitics in the die-to-die interconnects, which helps further reduce power and latency. Intel said Direct, which is complementary to Omni, will be ready for production use by 2023.

What It Means for Intel

As part of its new IDM 2.0 strategy under CEO Pat Gelsinger, Intel is building a foundry business to make chips on contract for other vendors and even rivals, a move that puts it in direct competition with foundry giant TSMC.

But winning major customers for its foundry business could take years. Intel is playing from behind TSMC, which should build chips more advanced than Intel's for at least three more years. Semiconductor firms tend to work very closely with their foundries to dial in designs ahead of production. Changing foundries — or working with a second contract chipmaker for dual-sourcing purposes — is usually a long and expensive endeavor.

But rolling out its advanced packaging tools as a service could give Intel a foot in the door with new customers, even if they choose to buy their most advanced chiplets from TSMC or Intel's other foundry foes. Intel said last month that Amazon AWS—which has designed a series of server chips called Graviton to replace some of Intel's chips in its cloud data centers—has agreed to adopt Intel’s advanced packaging at some point in the future.