The Most Frequently Asked MIPI I3C Questions—Answered

What you’ll learn:

- How MIPI I3C relates to I2C.

- How MIPI I3C Basic compares to the full I3C specification.

- How and where MIPI I3C is used today.

MIPI I3C, designed as the successor to the hugely popular I2C interface, is the MIPI Alliance's lightweight interface for easily and cost-efficiently connecting peripherals such as sensors, actuators, controls, and simple UI components to application processors. Products for these processors range from smartphones to wearables to systems in automobiles and server environments.

I3C comes in two flavors: the full I3C specification, available to MIPI Alliance members, and the royalty-free I3C Basic version, which supports all of full I3C specification’s core functionality and is publicly available for download.

Updated versions of both the full I3C and I3C Basic specifications were released in September 2021. In this article Tim McKee, chair of the MIPI I3C Working Group, answers the most frequently asked questions about the I3C interface.

How is MIPI I3C related to I2C, and what are the benefits of I3C compared with I2C?

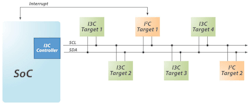

MIPI I3C was designed as the direct successor to I2C. Although I2C has been widely implemented, it's now more than 35 years old, and recent trends have posed new challenges for it. Data bandwidth requirements are on the rise, miniaturization is more and more necessary, and devices require even lower power consumption than before. MIPI I3C was developed specifically to address these issues while maintaining backward compatibility with I2C to support mixed use of I2C and I3C components within a device (Fig. 1).

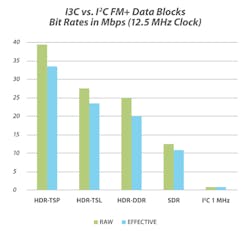

Put simply, I3C is faster, requires fewer pins and wires, and uses less power than I2C. For example, I3C supports a standard raw data rate of up to 12.5 Mb/s with 12.5-MHz clock using single-data-rate (SDR) mode. All of these features help improve the wide variety of devices that can utilize I3C.

They’re especially useful for products like next-generation Industrial Internet of Things (IIoT) devices. Common requirements for such devices include the need to connect many peripheral components (sensors, touchscreens, etc.), very low power consumption, and compact design, all of which are facilitated by fewer pins and wires.

How does I3C Basic compare with the full I3C specification?

MIPI I3C Basic was designed to facilitate access and adoption of the interface. Because of I2C's use in a vast array of devices, we saw the need for a version of I3C that could be implemented broadly beyond MIPI's membership under a royalty-free licensing environment. While not identical, I3C and I3C Basic are very similar, as I3C Basic bundles the most commonly used features of I3C.

In the most recent versions of the specifications, we reduced the differences between them even further by bringing many of the features from the full I3C specification into I3C Basic. For instance, two new high-data-rate (HDR) modes in I3C Basic enable the use of different clock and data-transmission models, so we can now increase the raw data throughput up to 25 Mb/s (with a 12.5-MHz clock using HDR-DDR mode) on a single lane. That's a huge leap forward.

What are the key features supported by I3C?

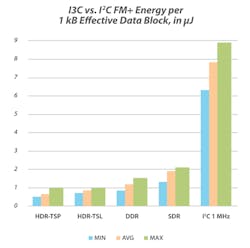

I3C provides a cost-effective, simple, and flexible two-wire interface and is designed to balance the need for higher data speeds with power efficiency (Fig. 2). It leverages CMOS (complementary metal-oxide semiconductor) I/O, as well as minimizes pin counts and the number of signal paths between components.

In addition, I3C supports a data rate of up to 12.5 Mb/s using its simplest mode of operation, and it includes options for higher-performance, high-data-rate modes that can provide speeds in excess of 30 Mb/s in single-lane mode. It consumes low amounts of energy per bit transported, allowing for these high speeds without sacrificing a low-power design (Fig. 3). For example, high-speed batch data transfers contribute to minimizing power consumption, as does allowing components to send infrequent bursts of data.

I3C supports in-band-interrupts (IBIs) to negate the need for additional physical lanes for interrupt signals. Some of the newer features include an option for extensible use of extra bus lanes to support a dual- or quad-lane configuration for up to 4X the speed increase of a single lane, future-proofing the interface for forthcoming greater speed requirements.

On top of that, a feature for standardized target reset enables better recovery from error conditions. This feature refines the specification’s ability to reset peripheral devices. It supports different levels of reset, from resetting only an I3C peripheral within a target to resetting the whole target device. This precision facilitates better recovery from error conditions by allowing a controller to reset only the selected targets without resetting any others.

Designers can learn more about I3C and I3C Basic and how their features compare, as well as access the specifications, by visiting the MIPI Alliance website. For instance, with the release of versions 1.1.1 of the specifications, we've updated our FAQs and released two new application notes—one on I3C’s Hot-Join feature and one on integrating virtual devices and targets.

Where is I3C being used today?

I3C Basic has already been adopted by JEDEC in its Sideband Bus and DDR5 standards. The MIPI Alliance also is actively working with DMTF (Distributed Management Task Force), ETSI (European Telecommunications Standards Institute), and TCA (Trusted Connectivity Alliance).

We hope to foster collaboration between many different organizations to continue to align I3C with the needs of the broader industry, and these collaborations with incredible organizations are helping us achieve that goal. Plus, whenever I3C Basic is adopted by another organization, it results in a richer ecosystem and fosters more interoperability within the broader industry.

Further, I3C can be used as a command-and-control interface for MIPI CSI-2 image sensors using the MIPI CCI (Camera Control Interface). Or, in the newest version of CSI-2 (v4.0 released to members in December 2021), it can be used as the principal transport channel for a camera sensor, negating the need for a physical-layer interface.

Use of CSI-2 over I3C leverages a new feature in the CSI-2 specification called AOSC (Always-On Sentinel Conduit), which enables ultra-low-power, always-on vision inferencing by an integrated or external digital signal processor. In turn, this allows a low-power host device to be always on, always monitoring its surrounding environment and waking the application CPU only when a relevant event happens. AOSC enables MIPI CSI-2 frame transport and bidirectional control using I3C.

In addition, the MIPI Debug for I3C specification developed by the MIPI Debug Working Group uses I3C to transport debug controls and data between a debug and test system and a target system. I3C also is used in the MIPI Touch family of specifications.

What software tools are available to help support implementation of I3C?

MIPI has created several different tools to help you when using I3C, whether the full version or I3C Basic. First, there’s the MIPI I3C Host Controller Interface (I3C HCI), which defines a common set of capabilities for the host controller and the software interface. We’ve also developed an I3C HCI driver for Linux and released it to the open-source community. And there’s MIPI Discovery and Configuration (MIPI DisCo) for I3C, which is a software framework designed to simplify the software integration of peripheral devices that use I3C.

How do I ensure interoperability between MIPI I3C implementations?

The first method is to use MIPI’s standard I3C conformance test suite, which is designed to ensure interoperability and compatibility between different vendors’ implementations. The test suite also is publicly available on the MIPI website.

MIPI I3C HCI is a huge help in this regard, too. With the I3C HCI, application-processor vendors gain a consistent method for interfacing to I3C, eliminating the need for product-specific I3C drivers. Instead, vendors, developers, and distributors can offer generic I3C drivers that are portable across hardware platforms.

It includes several optimizations based on typical usage and allows for vendor-specific extensions and optimizations. This also helps to control cost and complexity, freeing designers to focus their efforts on developing applications instead of interfaces. In addition, it broadens the scope of I3C implementation, since I3C HCI makes it easier for vendors and developers to integrate support for I3C for applications that are more than simple sensor devices.

The availability of the I3C HCI driver in the Linux kernel is of similar benefit. By defining device-specific operations for compliant I3C host controller hardware implementations from multiple vendors, the driver simplifies integration of I3C-based components for the global Linux developer community. The driver has been available in the Linux upstream source distribution since version 5.11 of the kernel.

Also, I3C Basic intellectual property (IP) is already available from multiple vendors, as are I3C conformance testing and verification IP test suites.