Solving DRAM’s Row Hammer Problem Using Vertical Epitaxial Transistors

What you’ll learn

- What is DRAM’s row hammer problem and why is it important?

- How vertical epitaxial transistors solve the problem.

- How Spin Memory’s Universal Selector works.

- How the Universal Selector can improve DRAM array density up to 35%.

So, what’s an MRAM company like Spin Memory doing in DRAM territory? It turns out that developing hyper-dense, high-performance MRAM storage has a lot to do with vertical epitaxial transistors, which can be quite useful in DRAM design. In particular, they can eliminate row hammer attacks that can be chronic in newer DRAM designs.

First a few basics. DRAM, unlike static memories, require a refresh cycle to maintain the contents of the memory cells. Forego refresh too long and the contents become junk. Conventional systems prevent this from happening with regular refresh cycles, so the contents don’t degrade sufficiently to cause errors.

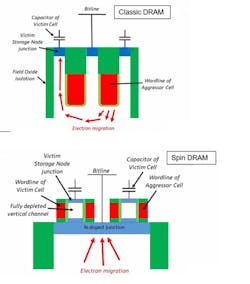

Still, there’s degradation, and even nearby accesses can affect adjacent rows of data. Row hammering is a technique of rapidly cycling nearby rows (Fig. 1). For system attackers, the trick is to run these transactions near data they want to corrupt, causing the software to fail in a fashion that the attacker can exploit. The solution is to isolate the rows such that nearby transactions have minimal effect, allowing the regular refresh cycles to maintain the data.

“Row hammer is one of the leading issues in DRAM reliability and security, and has long been a frustrating plague on the memory industry. As DRAM’s longstanding major disturb problem, row hammering is only becoming more of a problem as cells shrink,” said Charlie Slayman, IRPS 2020 technical program chair. “Spin Memory’s Universal Selector offers a novel way to design vertical cell transistors and has been presented to the JEDEC task group evaluating solutions to the row hammering problem.”

There have been some software approaches at mitigating row hammering effects, but it tends to be like playing a game of whack-a-mole with attackers. A hardware solution is more effective.

The Universal Selector

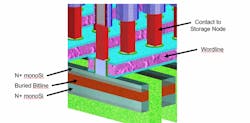

Spin Memory’s Universal Selector uses a vertical epitaxial transistor architecture (Fig. 2) that’s also used to create MRAM and 3D NAND memory. Spin Memory’s solution is applicable to two-terminal devices like DRAM as opposed to other techniques that target four-terminal storage devices, which tend to be larger. The implementation is built around a vertical-conduction, selective-epitaxy, monocrystalline channel. Rows are effectively isolated, thereby preventing row hammer attacks.

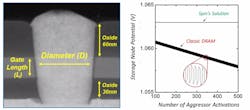

Of course, just mitigating attacks on DRAM is useful, but the Universal Selector architecture provided by Spin Memory has other advantages, especially as developers continue to scale down chip designs. The approach improves DRAM soft-error rates in general. The 4F2 (4F2) DRAM bitcell configuration (Fig. 3) can also improve array density by 20% to 35%.

The technique is applicable for emerging memory technologies including MRAM, ReRAM, and PCRAM. Here, the Universal Selector enables the creation of 1T1R memory bitcells of 6F2 – 10F2 (6F2 – 10F2). This translates to up to 5X more memory in the same area as a more conventional approach while only requiring minimal wafer-processing costs.

“Today’s most innovative and demanding technologies need more advanced memory to keep up with computing demands. Speed and reliability are necessary for complex applications running at the edge, such as autonomous vehicles or health wearables—where accurate and real-time decisions could make the difference between life and death,” said Tom Sparkman, CEO of Spin Memory. “Our latest breakthrough innovation allows for exciting new advancements and capabilities for these technologies, in addition to pushing MRAM into the mainstream market.”

Spin Memory isn’t in the DRAM business, but licensing the technology is a way to help DRAM vendors improve their product especially as we move into higher densities and smaller transistors.