Microchip Ups Ante With New Ethernet PHYs for Data Centers

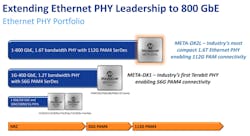

Microchip Technology rolled out a line of 1.6-Tb/s Ethernet PHYs with double the bandwidth of its previous generation, as it looks to get inside more of the switches, routers, and other networking gear in data centers.

Microchip said the new Meta-DX2L Ethernet PHYs could support data rates from 1 Gb/s up to 800 Gb/s. It is upgrading from 56G PAM4 SerDes technology in its previous generation of chips to the latest 112G PAM4 SerDes to transfer data between circuit boards, through connectors, across backplanes, and over copper cables and pluggable optical modules at the data rates required by telecom giants and cloud companies.

Babak Samimi, vice president of the communications business at Microchip, said the Meta-DX2L “doubles the bandwidth of previous solutions on the market while establishing a new level of power efficiency.”

The chips contain 32 112G PAM4 SerDes lanes that are programmable in a way that allows customers to save power over short-reach connections and bolster performance over long-reach copper cables (Figure 1). Microchip said the Meta-DX2L reduces power per port by more than one-third compared to its predecessor. They also occupy a smaller area, making it possible to pack more devices in a given power envelope.

The amount of data traveling within data centers is on pace to grow by 40% every year for the foreseeable future, driven by the rollout of 5G networks and the colossal cloud data centers run by the likes of Amazon, Google, and Microsoft. Microchip said that switches, routers, and other boxes of networking gear that coordinate these systems need higher bandwidths, more port density, and flexibility to handle the deluge of data.

The Meta-DX2L will sit inside networking switches that handle the logistics of transferring data around vast warehouses of servers or high-end routers that ferry information between the switches themselves. The chips, which support Ethernet ports at any data rate from 1 to 800 Gb/s, can also be integrated into server cards that plug into modular (or non-modular) switches or routers, connecting both sides of a backplane.

The Meta-DX2L, which tolerates industrial-grade temperatures, can also be used on the front panels of optical modules that use fiber to ferry data around data centers and copper cable assemblies that attach directly to the ports in switches and routers. While the family no longer supports the FlexE protocols, Microchip said Meta-DX2L could run several other networking protocols, including FlexO and Fibre Channel.

“The industry is transitioning to a 112G PAM4 ecosystem for high-density switching, packet processing, and optics,” said Bob Wheeler, principal networking analyst at The Linley Group, in a statement. “Microchip’s Meta-DX2L is optimized to address these demands by bridging line cards to switch fabrics and multi-rate optics for 100 Gb/s, 400 Gb/s, and 800 Gb/s connectivity."

This new chip also helps to address the signal integrity challenges within the sprawling networks at the heart of data centers. Many of the switches used in data centers are swapping out 56G PAM4 SerDes in favor of 112G PAM4 SerDes. But doubling the signaling rate is creates signal integrity issues. When 56G PAM4 SerDes replaced 28G NRZ, both standards worked at the same data rate, and therefore the signal loss stayed the same. The trade-off was that it became more challenging to keep the “eye” open.

The term “eye” refers to the pattern of a digital signal traveling around a circuit board or through connectors and cables. When using an oscilloscope during testing, the pattern looks like an eye. The larger the opening of the eye, the less signal distortion. As telcos and cloud vendors upgrade to 112G PAM4 interconnects in the data center, signal loss doubles. To preserve signal integrity, server manufacturers are turning to more advanced board materials and the use of chips called retimers to recondition signals and amplify them.

“At 112G PAM4, the signal integrity challenge is probably bigger than it was even in the previous generation,” Ben Lake, product marketing manager of Ethernet PHY products at Microchip, told Electronic Design.

Microchip said the Meta-DX2L could serve as a retimer, which is used to recover data that has been distorted, reconstruct it, and send it out over longer distances. These new chips also have the flexibility to function as forward or reverse “gearboxes” that convert a signal traveling over the network at one rate (for instance, 28G NRZ or 56G PAM4) and translate it to another (such as 56G PAM4 and 112G PAM4), according to Microchip.

The chips have a highly configurable crosspoint feature that allows them to connect to many different types of optics and data paths in a single design, simplifying the routing of components on the circuit board (PCB).

The Meta-DX2L also features forward error correction (FEC) termination, monitoring, and conversion for different data rates.

As cloud giants and other hyperscalers clamor for more bandwidth, Ethernet PHYs need to consume less power and fit into smaller packages. Microchip said Meta-DX2L comes in what it calls the most compact package in the category, measuring only 23 × 30 mm. The more rectangular shape means more chips can be placed side by side in a system compared to the square form factor in its previous generation of Ethernet PHYs. These space savings help deliver the port densities needed by system designers, the company said.

Power efficiency is another priority Microchip addressed in the Meta-DX2L. The chip reduces the power per port by 35% compared with the previous Meta-DX1, which was said to be the first 1.2-TB/s Ethernet PHY.

Microchip said the new chip is also targeted at new 5G networks, which have very tight timing requirements. The Meta-DX2L features “constant latency” data paths to cut down on timing delays in 5G infrastructure.

Microchip is not alone in upgrading its Ethernet PHYs for data centers. In June, Marvell introduced its 1.6-TB/s Ethernet PHY with 112G PAM4 SerDes technology based on the 5-nm node to support the higher bandwidth required by the largest cloud data centers. Marvell said the Alaska C PHY brings double the bandwidth of its prior generation of chips to high-density switches with 400G and 800G Ethernet ports.

Microchip is trying to stand out by offering reference designs that give customers a blueprint for building a complete system, from the Ethernet PHY to secondary chips such as voltage regulators and clock buffers (all belonging to Microchips portfolio). These parts are all pre-validated as a system to help customers bring server gear to market faster. Complementing the Meta-DX2L is a complete software development kit (SDK).

Microchip said customers could reuse their designs from telecom routers to data-center switches, improving time to market thanks to the PHY's many different operating modes and common hardware and software platform.

The Meta-DX2L is expected to start sampling in the fourth quarter of 2021.