This article is part of TechXchange: RISC-V: The Instruction-Set Alternative

What you’ll learn:

- Why Imagination is getting back into the CPU business.

- What does the Catapult RISC-V core look like?

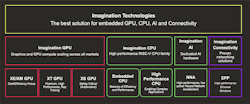

Imagination Technologies is known for its PowerVR GPU cores—in fact, the MIPS RISC cores were once part of its portfolio. These were sold to Tallwood MIPS, which was later acquired by Wave Computing. Imagination Technologies has filled this void with a new series of cores based on the RISC-V instruction set (Fig. 1). It joins others that are part of the RISC-V Foundation, which fosters RISC-V technology.

Having a balanced portfolio allows Imagination Technologies to deliver a complete solution rather than just a portion. It has the expertise in CPU design and excels in other areas as well. Its latest GPU delivers ray-tracing support for mobile devices, a technology that’s been challenging even for desktop PCs.

The Imagination CPU targets RISC-V applications for embedded applications as well as high-performance solutions. Other components in its toolbox include artificial intelligence (AI) with low-power neural-network acceleration and communication support for high-performance Ethernet. Its expertise in safety-critical applications such as automotive is well-known, too.

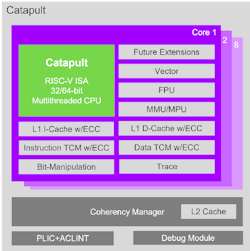

The Catapult cores implement the scalable RISC-V instruction set (Fig. 2). As with most RISC-V designs, there’s a mix-and-match approach depending on what features are needed for a particular application.

The Catapult family is still growing, starting with 32- and 64-bit in-order platforms designed for real-time applications. There are four distinct families right now, including dynamic microcontrollers, real-time embedded CPUs, high-performance application CPUs, and functionally safe automotive CPUs. The microcontrollers are already shipping in automotive applications in conjunction with Imagination’s functional-safety GPU cores.

Right now, the multithreaded family supports up to eight asymmetric, coherent cores per cluster with the ability to integrate custom instructions and accelerators. Multicore, 64-bit, out-of-order (OoO) instruction execution solutions are on the roadmap. End-to-end security for ISO/SAE 21434 and automotive safety standards like ISO 26262 are part of the mix, something that Imagination has been doing with their other cores for years.

RISC-V-compatible compilers are available from a number of vendors and open-source projects including GCC and LLVM. The Catapult Studio is an IDE based on the open-source Visual Studio Code from Microsoft. Full source is available for Linux, including reference boot loaders, kernel, and file system. The cores are compatible with the GEM5 simulator.

Read more articles like this at the TechXchange: RISC-V: The Instruction-Set Alternative