This article is part of TechXchange: Chiplets - Electronic Design Automation Insights

What you’ll learn

- What are chiplets?

- What is the Universal Chiplet Interconnect Express (UCIe)?

- Why UCIe matters.

The idea behind chiplets and standardization isn’t new, but rather a logical progression in terms of miniaturization. Bus standards like the Industry Standard Architecture (ISA) bus used on the stackable PC/104 board form factor enabled the creation of a vast ecosystems with many parties providing compatible boards that worked together. PC/104 has since migrated to PCI Express (PCIe).

Even smaller form factors like MiniPCIe and M.2 allow for modular upgrades to occur on small systems. However, moving down to the chip level requires a whole new approach compared to plugging in boards and modules or laying out a printed circuit board (PCB).

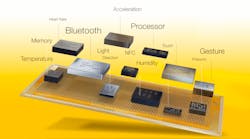

Actually, a tiny PCB isn’t far from the truth as chiplets are essentially die that we mounted on a silicon interposer. Technologies like high bandwidth memory (HBM) are implemented using this technique since the memory and other logic are on separate dies. Check out our chip packaging video series for more details on chiplets and chip packaging in general. It also covers multichip modules (MCMs) and system-in-package (SIP). Our Path to Systems series addresses SIP design techniques and issues.

The UCIe Standard

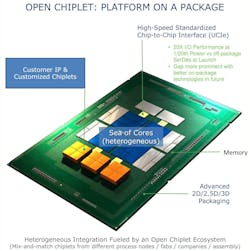

Which brings up the latest announcement on the Universal Chiplet Interconnect Express (UCIe) standard. It’s built around PCIe, but at the chiplet level. The idea is to provide a standard interface for chiplets. So, it’s simply a matter of choosing which chiplets were required for an application and then using layout tools to handle logical positioning and connections between chiplets in much the same way as PCBs are now laid out (see figure).

Interfaces like Arm’s Advanced High-Performance Bus (AHB) work for custom ICs and similar standards can be used on FPGAs. Still, they’re not as useful for chiplets where interfaces like PCIe make sense.

CXL and PCIe

The UCIe standard is based on PCIe and Compute Express Link (CXL). The latter builds on PCIe but adds coherent cache support, allowing it to handle memory as well as providing CPU-to-CPU and CPU-to-device communication. Not as many CXL solutions are generally available, as CXL 2.0 requires PCIe 5.0, though that’s changing.

CXL and PCIe can handle large amounts of data by grouping multiple serial links together. This can be advantageous for some UCIe-based chiplets, but more often, a single PCIe lane is all that’s needed.

The approach will allow reduced time-to-market and simplify selection of functional components. It also should simplify chip design since the bulk of the functionality is found in the chiplets that are standardized. This will make it more economical for smaller projects or smaller companies to have a custom chip made by using die from a variety of chip vendors. Likewise, layout tends to be easier with a single set of power and communication channels for each chiplet.

The approach also makes the job of mixing different sources of devices in a system-on-chip (SoC). Each chiplet would need power, potentially some basic I/O for off-chip interfaces, and a PCIe connection or arbitrary width to communicate with other chiplets or switches in the SoC.

What may make this whole thing work is that the major players support the UCIe, including Advanced Semiconductor Engineering Inc. (ASE), AMD, Arm, Google Cloud, Intel Corp., Meta, Microsoft Corp., Qualcomm Inc., Samsung, and Taiwan Semiconductor Manufacturing Company (TSMC).

The advantage of this approach is that it mimics the PCIe/CXL interfaces found at the board level, which means that the same software stacks can be utilized. The only difference is the compactness provided by an SoC. It also means that the same architecture works for off-chip communication, and on-chip communication can be expanded by using PCIe switch chiplets.

For more details on chiplets, check out our TechXchange on chiplets that also includes the Chiplets – Electronic Design Automation Insights webinar.

Read more articles in TechXchange: Chiplets - Electronic Design Automation Insights