What you’ll learn

- What is the Cortex-M85?

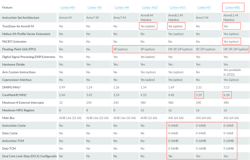

- How does it compare to the other Cortex-M family members?

Arm’s latest Total Solutions for IoT announcement included the release of the Cortex-M85, which fills out the high end of the Cortex-M family (Fig. 1). It specifically targets IoT applications that require security provided by the Armv8-M TrustZone implementation.

Developers also can choose to include the pointer authentication and branch target identification (PACBTI) extensions. This support is designed to mitigate security exploits like return-oriented programming (ROP) and jump-oriented programming (JOP) attacks.

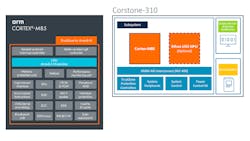

The Cortex-M85 supports Arm’s Helium artificial-intelligence/machine-learning (AI/ML) instruction augmentation (Fig. 2). The chip can handle half-, single-, and double-precision floating point like the Cortex-M55, which also supports Helium. Half-precision floating point is useful in reducing the overhead of AI/ML model manipulation.

In addition, the CPU can be paired with the Ethos-U55 micro neural processing unit (microNPU) in the Corstone-310 reference package. This is the basis for Arm’s Total Solution for Voice Recognition solution, although it’s equally applicable to other applications that can utilize the performance and AI/ML enhancements.

Performance Push

The design delivers 6.28 CoreMark/MHz—a significant bump even compared to the Cortex-M7. Part of the performance improvement is due to the use of on-chip memory caches. These are protected with error-correction-code (ECC) support. Developers also can take advantage of Arm Custom Instructions if all of these new features are insufficient to implement their secret sauce.

The Cortex-M85 incorporates the CoreLink DMA-350 direct-memory-access (DMA) controller. It can handle tightly coupled memory (TCM) and is useful for AI/ML and signal-processing applications.

Furthermore, the Cortex-M85 is supported by Arm Virtual Hardware emulations that allow developers to build software before delivery of hardware. Virtual hardware provides additional insights into the operation of the core that aren’t available in physical hardware.