Qualcomm Plans New Chips to Compete with Apple in Wearables

Qualcomm is stepping up the competitive pressure on Apple with plans to start selling a line of ultra-low-power chips specially designed for the booming smartwatch and wearables market.

According to the company, the new chips promise up to 2X faster with up to 50% longer battery life for smartwatches using Google’s Wear OS. Dubbed the Snapdragon W5 and W5+ Gen 1, the chips represent a huge generational leap for Qualcomm, which built them on the 4-nm node and moved to a new ultra-low-power architecture that draws less power and is smarter about how it consumes the battery power available to it.

Qualcomm’s global head of smart wearables, Pankaj Kedia, said both chips are designed from the ground up for wearables. It started working on the platform three years ago, even before rolling out its predecessor, the Wear 4100, stripping out anything unnecessary for the wearable market. It overhauled everything left to fit the unique features consumers want out of a smartwatch, such as always-on displays and day-long battery life.

"The wearables industry continues to grow and present opportunities across multiple segments at an unprecedented pace," he said, adding the W5+ and W5 platforms represent its “most advanced leap yet.”

Closing the Gap

While its Snapdragon Wear series powers the vast majority of Wear OS smartwatches, the chips generally have lagged behind the Apple-designed “S” series system-in-packages (SiPs) at the heart of the Apple Watch.

The company hopes the Snapdragon W5 and W5+ platforms will help electronics companies take the fight to Apple, which holds about 30% market share in smartwatches now, accounting for roughly half of global sales last year.

There are 25 devices in the pipeline based on the W5 and W5+ Gen 1 platforms, including smartwatches powered by Google’s Wear OS 3, the latest version of the Android maker's operating system for wearables.

Qualcomm is trying to lock down a larger slice of the smartwatch market that soared by 24% in 2021, with a record of more than 40 million units shipped in the fourth quarter last year alone, according to Counterpoint Research.

The company upgraded from the 12-nm node in its predecessor to the more advanced and more energy-efficient 4-nm process, putting it more on level ground with rivals Apple and Samsung in terms of process technology.

Hybrid Architecture

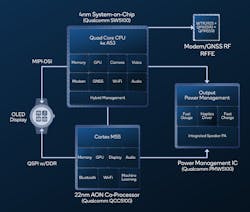

The W5+ has the same hybrid architecture as its previous generation, released in 2020. At the heart of the platform is the SW5100 SoC that handles more of the heavy workloads in wearables.

The processor features four Cortex-A53 CPU cores—the same CPU used in the previous two generations of its wearable platforms—clocking at up to 1.7 GHz. It also incorporates the Adreno 702 GPU that runs up to 1 GHz, a major generational leap over the previous 320-GHz Adreno 502 GPU. Also under the hood is a dual 16+16-Mpixel image signal processor (ISP) and 2133-MHz LPDDR4 RAM, as well as Wi-Fi, GNSS, and 4G LTE modem.

The W5+ Gen 1 is also paired with a secondary, ultra-low-power co-processor based on Arm’s Cortex-M55 MCU. The QCC5100 handles a host of the background work when the smartwatch or wearable is not in use.

That means smartwatches with the W5+ Gen 1 inside can run the vast majority of the time without turning on the main processor, giving it a big boost in terms of power efficiency and, thus, longer battery life, said Kedia.

When a user is interacting with a smartwatch, the W5+ takes advantage of the SW5100 so that they can send messages, make calls over voice or video, or scroll through rich real-time maps. Qualcomm said it upgraded the Cortex-M55 MCU so that it can run most everything else on the smartwatch when a user is not actively interacting with it. That includes the always-on display, notifications, audio, and health and sleep tracking.

Based on the 22-nm node and clocked at up to 250 MHz, the co-processor contains the display driver and separate graphics processor to run always-on displays that show the time. The co-processor also adds an ultra-low-power Bluetooth 5.3 radio that was previously plugged into the main SoC, said Kedia.

Qualcomm said the MCU, which supports FreeRTOS, can also continuously run heart-rate sensors, gyroscopes, accelerometers, thermometers, and other sensors that are equipped to help monitor fitness, sleep, and health.

In addition, the co-processor delivers enhanced on-device machine learning with Arm's Ethos-U55 microNPU. Other building blocks in the W5+ Gen 1 include new power-management (PMW5100) and radio-frequency ICs.

Power Conscious

The W5+ Gen 1 is ideal for high-end smartwatches, but the W5 Gen 1 (which comes without the co-processor) is designed more for “segment-specific wearables” targeting seniors and children or even medical wearables.

With the move to more advanced manufacturing nodes, the SW5100 fits in a 30% smaller footprint. Other improvements at the system level result in 35% space savings for the chipset and 40% in the circuit board. That will make it possible for electronics makers to produce smaller, thinner smartwatches and wearables.

To keep power consumption in check, low-power "islands" are also baked into the main processor so audio, GNSS, and Wi-Fi—all coordinated by the Cortex-M55 MCU—can run without waking up other components.

To further bolster power efficiency, the W5+ Gen 1 uses “deep sleep” and “hibernate” states that shut down large portions of the Cortex-A53 SoC when workloads only require a minimum of computing power. These power-saving modes disable most of the processor except for the RAM or flash, allowing the W5+ to run on less than 1 mA of standby power overall.

Packaged with a newly designed power-management IC (PMIC) from Qualcomm, all of the upgrades translate to an average of 50% less power consumption versus the previous generation chips—the Wear 4100.

According to Qualcomm, that means smartwatches with a 300-mAh battery can go from 28 to 43 hours of battery life, while a cellular-connected smartwatch with a 600-mAh battery can last 50% longer at 72 hours.

“Every bone in its body is designed for low power,” explained Kedia. “We have reimagined it at every level.”